evilguy

Full Member level 4

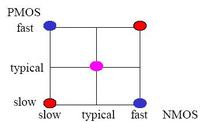

corner analysis

is process corner show process variation in the process? for example, if we do corner analysis in TSMC 0.18µ process, can we conclude that process variation will occur only in the range of corner analysis? i'm a bit confuse a bout this two term. can someone explain to me what are this to represent.

is process corner show process variation in the process? for example, if we do corner analysis in TSMC 0.18µ process, can we conclude that process variation will occur only in the range of corner analysis? i'm a bit confuse a bout this two term. can someone explain to me what are this to represent.