Junus2012

Advanced Member level 5

Hello friends,

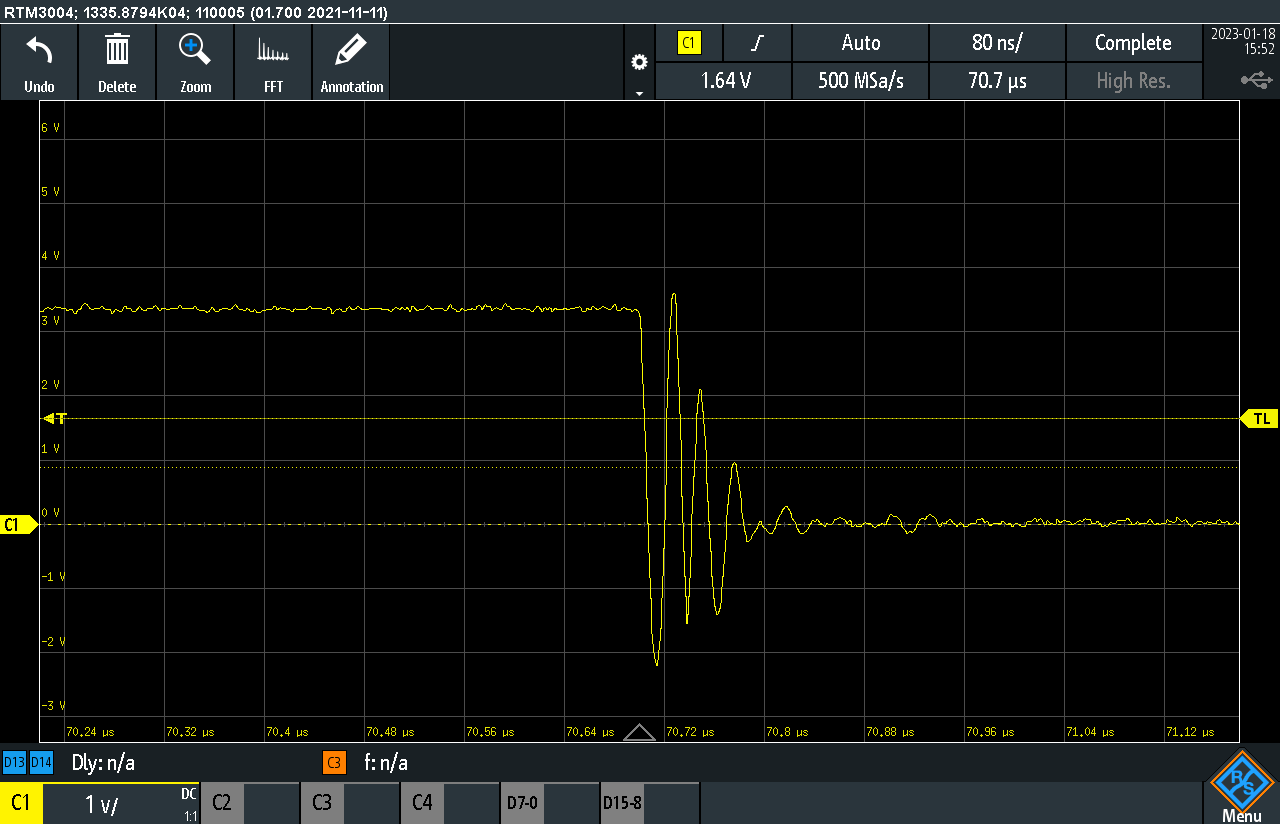

I have in my digital circuits outputs like digital signal from FPGA board or simple logic IC a practical bouncing when the output switch from one logic state to another state (from 0 to 1 or 1 to 0) as seen from the images below.

I have read from digital buffer data sheet a general note that if the output current drive capability is high, then this bouncing will be expected. I want to know from your experience how you treat it, because what I see from my eys that these over or undershoot magnitude are big enough to trigger the next logic stage.

The other question, why these peaking were not predictable by Cadence simulator.

Thank you in advance

Regards

I have in my digital circuits outputs like digital signal from FPGA board or simple logic IC a practical bouncing when the output switch from one logic state to another state (from 0 to 1 or 1 to 0) as seen from the images below.

I have read from digital buffer data sheet a general note that if the output current drive capability is high, then this bouncing will be expected. I want to know from your experience how you treat it, because what I see from my eys that these over or undershoot magnitude are big enough to trigger the next logic stage.

The other question, why these peaking were not predictable by Cadence simulator.

Thank you in advance

Regards