Chinmaye

Full Member level 3

- Joined

- Jan 18, 2016

- Messages

- 164

- Helped

- 0

- Reputation

- 0

- Reaction score

- 1

- Trophy points

- 1,298

- Activity points

- 3,145

Dear all,

I am trying to model analog latch in verilog-a but have been unable to do it. The requirement is as follows

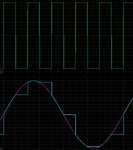

It is required to sample an analog value at positive clock cycle of CLK2 and hold the same value even during the negative clock cycle of CLK2.

Any leads??

I am trying to model analog latch in verilog-a but have been unable to do it. The requirement is as follows

It is required to sample an analog value at positive clock cycle of CLK2 and hold the same value even during the negative clock cycle of CLK2.

Any leads??