sherif96

Member level 4

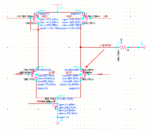

I am designing a balanced ota with cascode output stage attached is the circuit in a textbook and my ota schemaitc, however I am still new to IC designing I did not get the hang of all the basics yet, I am trying to bias all the transistors in the circuit and due to the assymetric second stage transistors I decided to adjust my circuit to be fully differential and add an extra common mode feedback circuit, to make the circuit fully differential i removed the current mirror in the real circuit at the bottom right, to have two identical branches - correct me if i am wrong- however the circuit is not biased correctly yet and some of the vdsat numbers are very high, any ideas?

vdd=1.2v

vn5=500mv

vp5=500mv

vn6=250mv

vp6=250mv

vdd=1.2v

vn5=500mv

vp5=500mv

vn6=250mv

vp6=250mv