dreamyboy_999

Member level 2

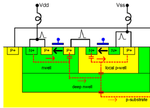

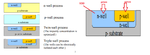

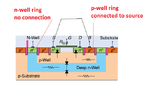

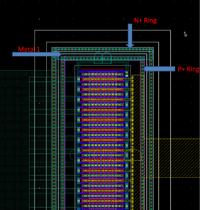

I assume in a triple well process, you can have isolated nmos devices by first creating an nwell and then creating the Pwell substrate inside the nwell. My question is: Where should the guard ring (which is an N+ ring connected to the surrounding nwell) connected? Does that need to be connected to the Pwell (body of the inside nmos transistor) or any other potential? (Vss or Vdd).