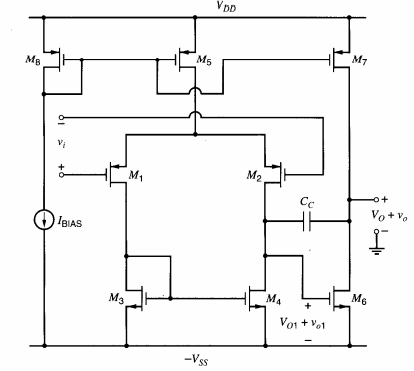

I am recently studying "Analysis and Design of Analog IC" by Gray, Hurst, Lewis & Meyer. In chapter 6, pg 428 for a design of a classical 2stage op-amp having PMOS differential inputs, there is a statement: "In MOS technologies, however, the gm*ro (intrinsic gain), the product is usually between about 20 and 100, reducing the gain per stage and sometimes causing the offset of the second stage to play an important role in determining the op-amp offset voltage." What does it mean, I am not able to understand this statement properly.