Lucast85

Member level 3

Hi everyone,

I've tryed to simulate some Infineon Mosfets by using differents models they provide on the website.

I'm interesed into RDS(on) value and into self-heating behaviour. During simulation I cannot reach the Rds(on) as declared on the datasheet. However by trying different Mosfets from other manufacturer I can measure the declared Rds(on) with the same test circuit.

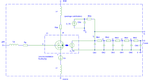

This is the circuit setup by using LTspice and IPB015N08N5 NMOS:

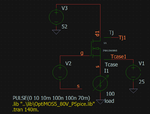

As you can see the Vgs is a pulse of 10V, the drain current is 100A (dissipative Isource, or load), and the case temperature is forced to be 25°C. The datasheet report a typical RDS(on) of 1.1 mohm but the simulation give me an RDS(on) of 2.15mohm (calculated as Vds/I1) when MOS is on.

Why? Any idea?

I've tryed to simulate some Infineon Mosfets by using differents models they provide on the website.

I'm interesed into RDS(on) value and into self-heating behaviour. During simulation I cannot reach the Rds(on) as declared on the datasheet. However by trying different Mosfets from other manufacturer I can measure the declared Rds(on) with the same test circuit.

This is the circuit setup by using LTspice and IPB015N08N5 NMOS:

As you can see the Vgs is a pulse of 10V, the drain current is 100A (dissipative Isource, or load), and the case temperature is forced to be 25°C. The datasheet report a typical RDS(on) of 1.1 mohm but the simulation give me an RDS(on) of 2.15mohm (calculated as Vds/I1) when MOS is on.

Why? Any idea?