rfub

Newbie level 6

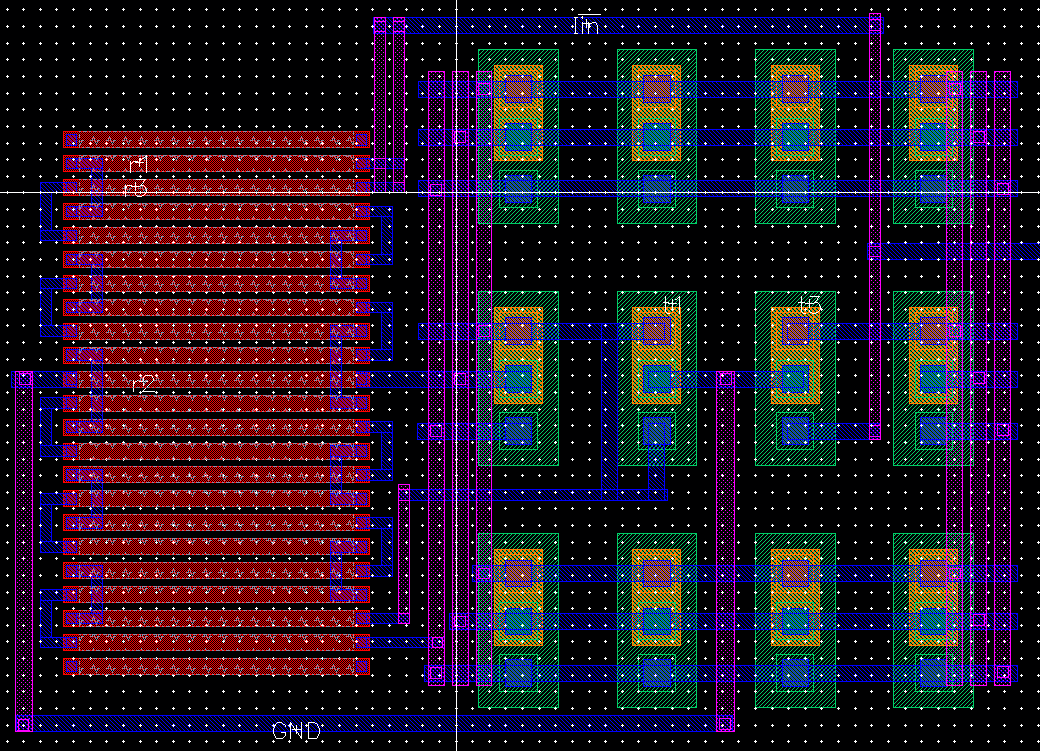

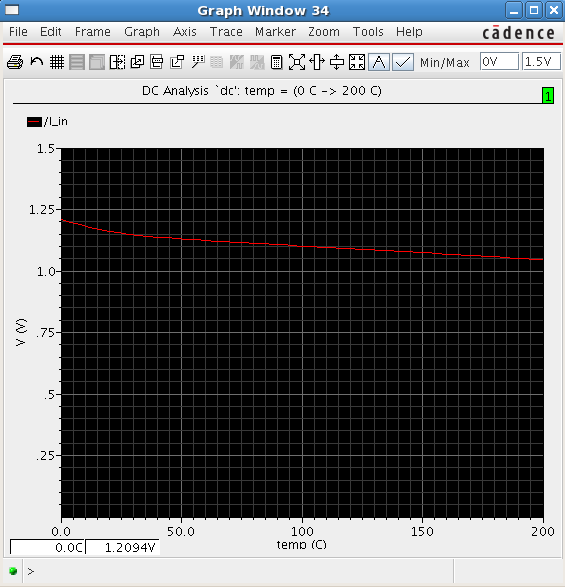

Hi all, I have a layout assignment about Widlar bandgap, I have no idea about how to do it, I'm willing to learn and it's really important to my future course work.

we are supposed to layout in Cadence Virtuoso, using NCSU_TechLib_ami16 technology.

I have several questions.

1. T1:T2:T3 should be 1:10:1, what parameters in the layout can determine the ratio?

2. Is there any tutorial of picture shows how to layout a bipolar transistor?

Thank you for helping.

we are supposed to layout in Cadence Virtuoso, using NCSU_TechLib_ami16 technology.

I have several questions.

1. T1:T2:T3 should be 1:10:1, what parameters in the layout can determine the ratio?

2. Is there any tutorial of picture shows how to layout a bipolar transistor?

Thank you for helping.