Jordon

Member level 1

- Joined

- Dec 25, 2022

- Messages

- 33

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 6

- Location

- Shanghai, China

- Activity points

- 265

Hi,

I am using TSMC 28hpc digital PDK to design some circuits.

When I running the DRC, I found some DRC errors because the spacing, and finally, I found the techfiles that innovus used is different from the DRC rule.

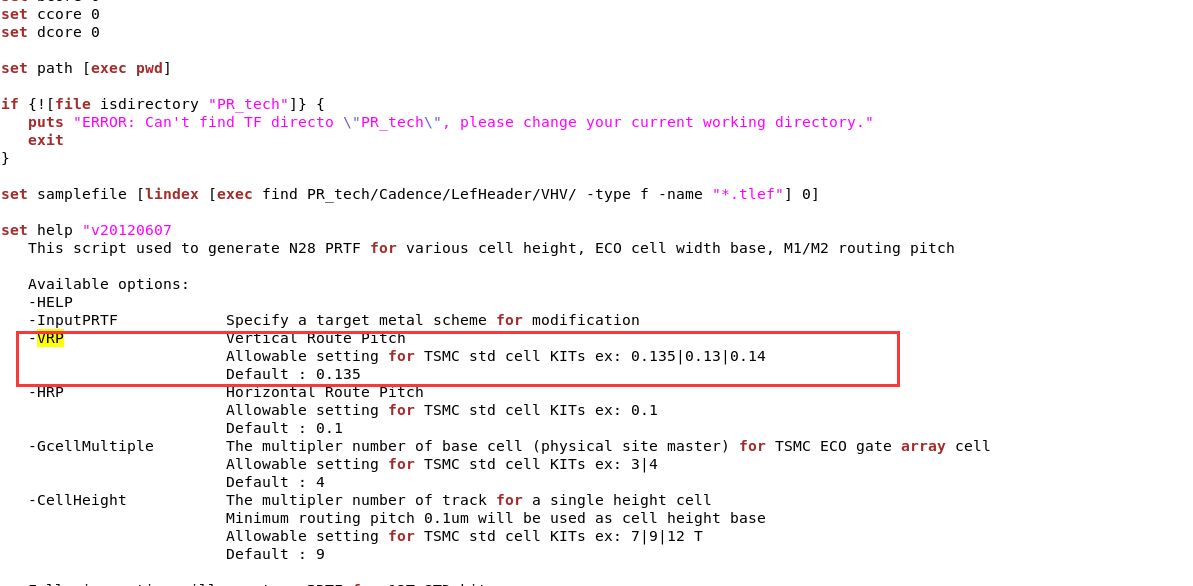

In DRC rules, the Vertical Route Pitch is 0.14, but in the techfiles, TSMC provide a GenPRTF.tcl, where exists three options for Vertical Route Pitch, 0.135, 0.13 and 0.14, as the screenshot shows.

So, why TSMC leave that useless(maybe) opyions "0.135" and "0.13" with the DRC setting is 0.14? It seems the options "0.135" and “0.13” will never be used if your circuits need to pass the DRC.

I am using TSMC 28hpc digital PDK to design some circuits.

When I running the DRC, I found some DRC errors because the spacing, and finally, I found the techfiles that innovus used is different from the DRC rule.

In DRC rules, the Vertical Route Pitch is 0.14, but in the techfiles, TSMC provide a GenPRTF.tcl, where exists three options for Vertical Route Pitch, 0.135, 0.13 and 0.14, as the screenshot shows.

So, why TSMC leave that useless(maybe) opyions "0.135" and "0.13" with the DRC setting is 0.14? It seems the options "0.135" and “0.13” will never be used if your circuits need to pass the DRC.