hioyo

Advanced Member level 4

Why is pulsed drain current higher than continuous drain current in MOSFETs?

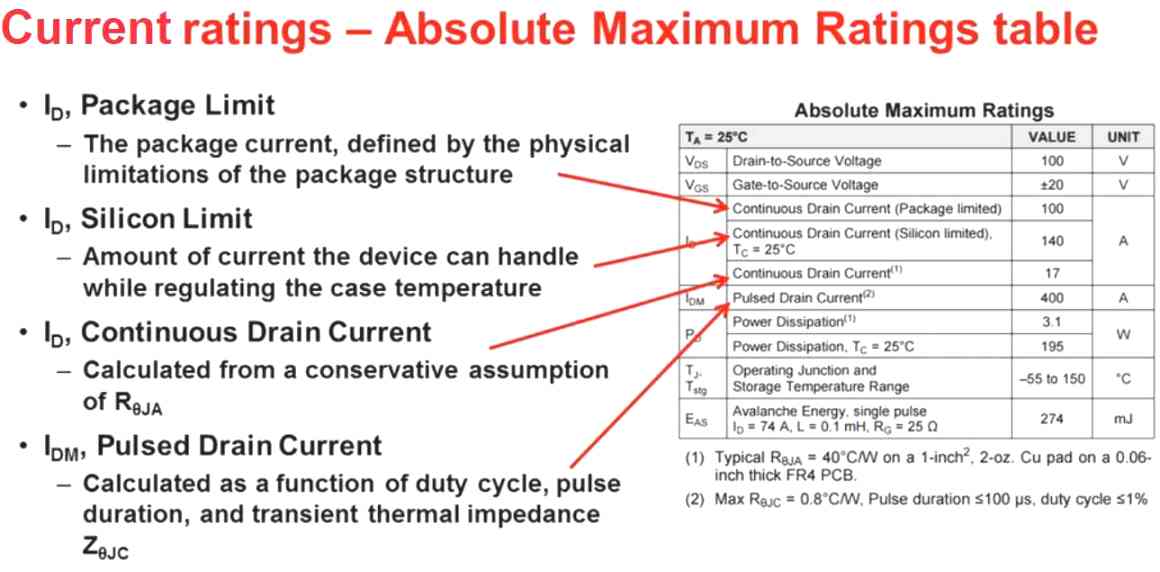

In MOSFET data-sheets, pulsed drain current is much higher than (by 4x) continuous drain current.

What is the reason behind thi

In MOSFET data-sheets, pulsed drain current is much higher than (by 4x) continuous drain current.

What is the reason behind thi