Singkwan

Newbie

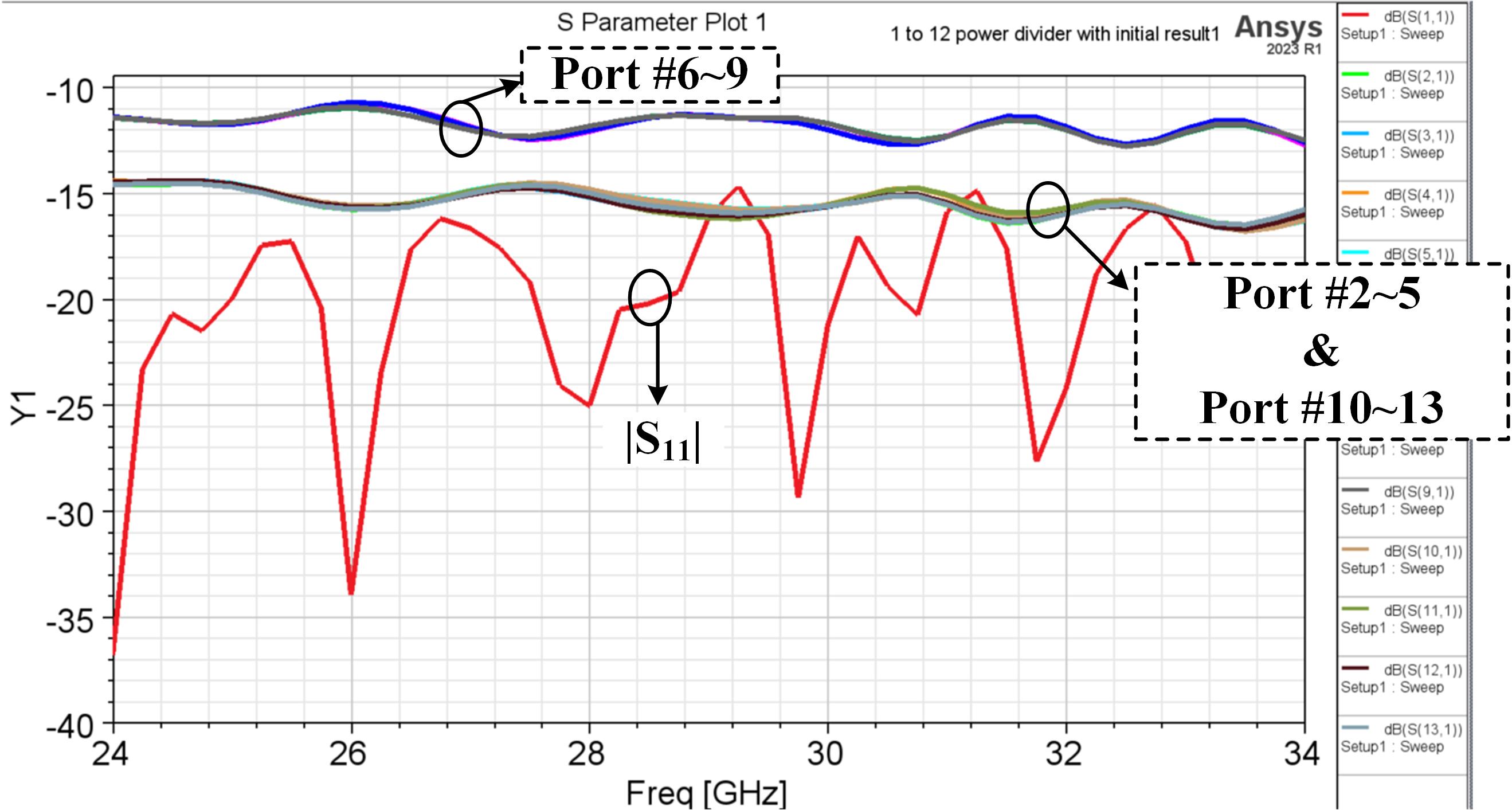

All power dividers shown as below figures have equal power distribution. Why is the output of the power divider I designed unstable? The S parameter exhibits wave like fluctuations.

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

I thought the same at first, but then I've realized that OP is more advanced and probably understands that. Most likely it is about... pass band ripple of this divider? Maybe there is a better term for microwaves.Hi,

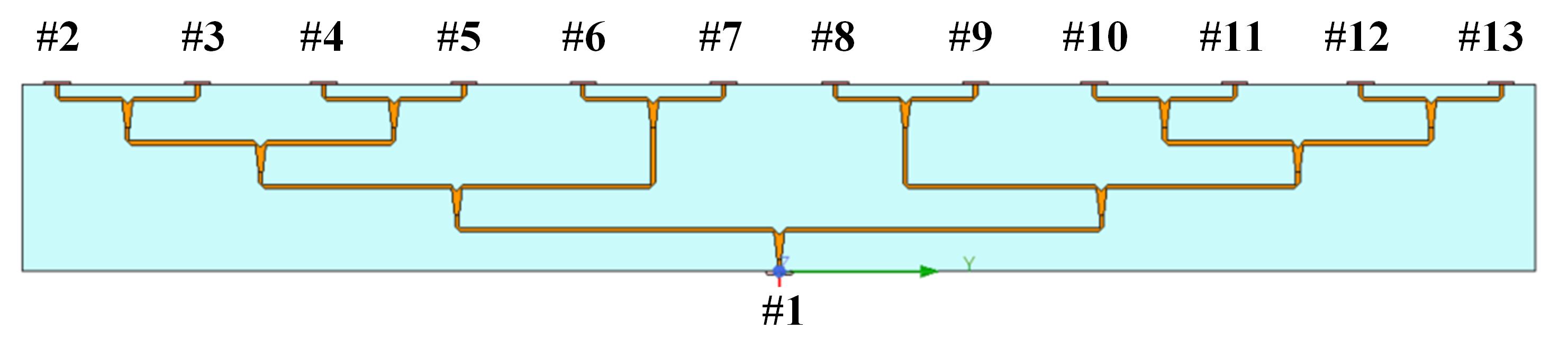

I´m not an expert, but when you start at input #1, then go left to the next divider.

This divider has two branches: On feeds 4 outputs: #2, #3, #3 and #4 while the ther branch feeds 2 outputs only #5 an #6.

now if the power is divided equally to each side, then the left side power is fed to 4 outputs, while the right side is fed to 2 output ...

so in the left case: power/4 and the right sied: power/2

Thus I guess the power at #6 and #7 is about twice the power of #2 to #5. so a plus of 3dB.

Klaus

Thanks a lot, [B]Georgy.Moshkin[/B].Looks ok to me.. But if its unacceptable for your application, I have few ideas:

1) Single divider still has mismatch. Have you tried to simulate single divider? If there is some small mismatch, it will work as 4 impedance transformers (e.g., path from port 1 to port 2). Try to simulate single divider by extending input port length by 90 degree (quarter wavelength) line and compare with unmodified one

2) I never worked with Ansys, but if it uses process called "Meshing", your grid size may be too coarse. Maybe your simulator used lower resolution grid because of larger PCB area. You need to check it by using some option to view generated finite element grid and see if your power divider geometry is still ok.

In my opinion, these "waves" are result of unwanted impedance transformation, and it repeats each n*180 degrees, when your frequency goes from 24GHz to 34GHz, phase length gradually "shrinks" and increases phase length of transmission lines.