mssong

Junior Member level 2

Why is the offset of my PLL so large?

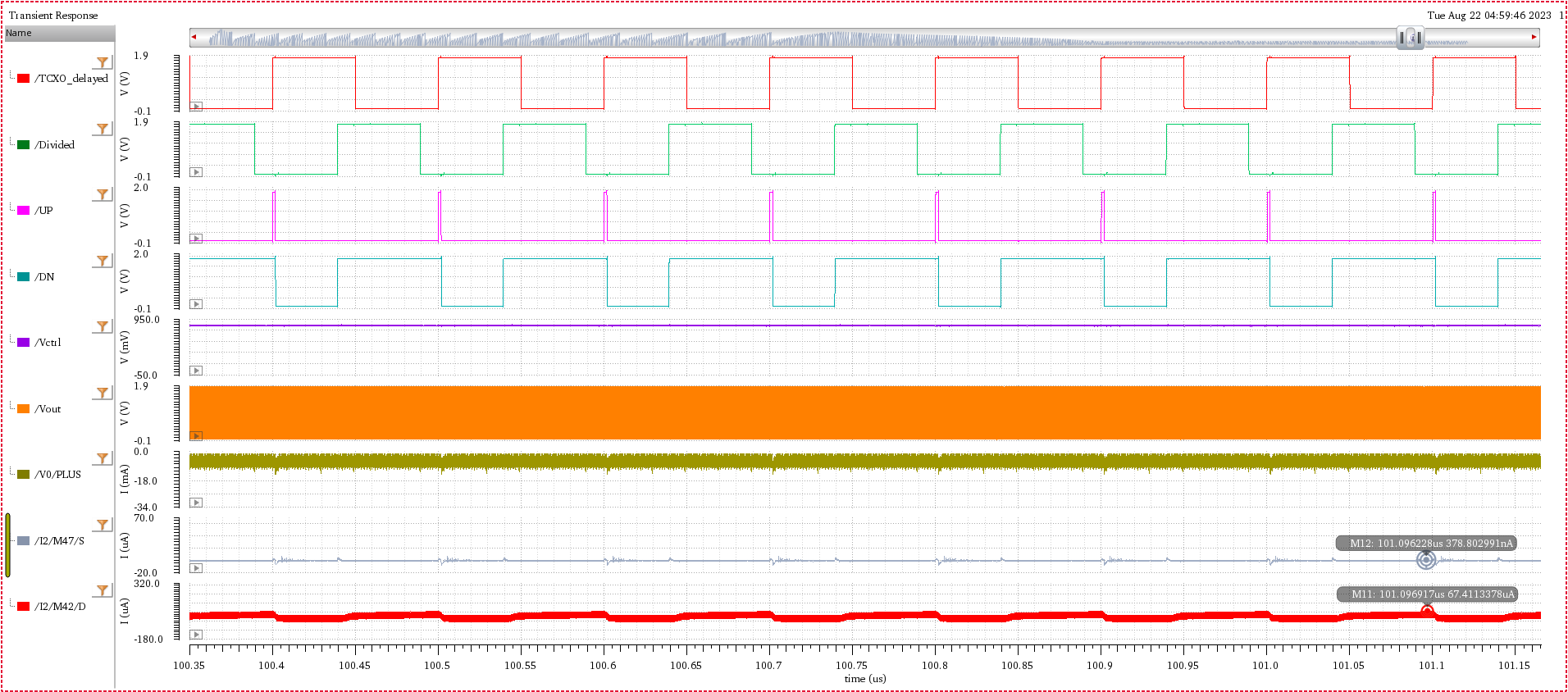

The waveform of the TCXO and the divided waveform

UP and DN signals

UP current and DN current

I have attached the waveforms.

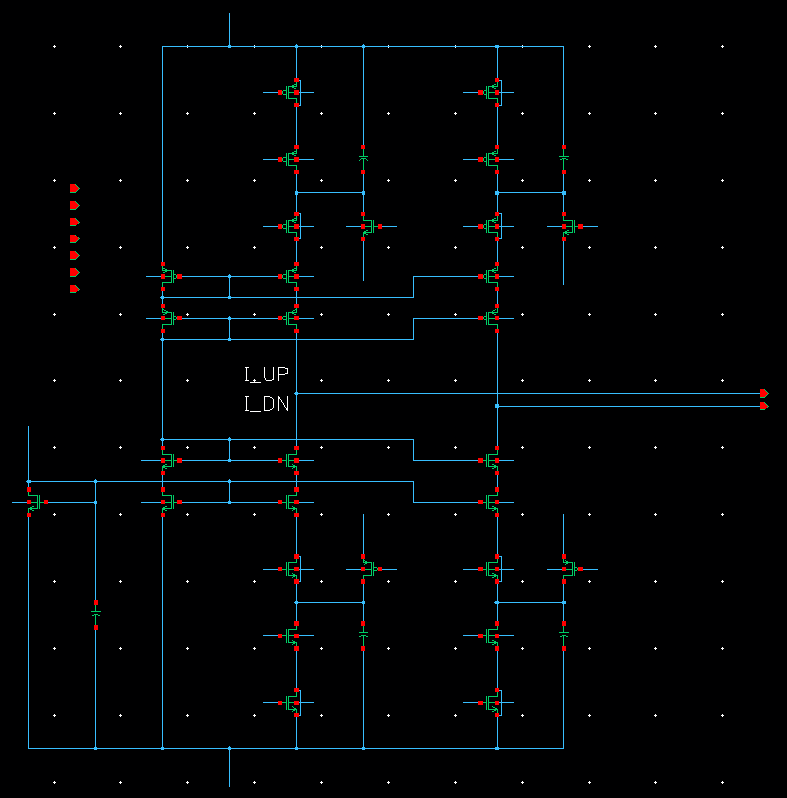

I have also attached the charge pump, vco type is LC. varacator cap is 200fF to 800fF.

The waveform of the TCXO and the divided waveform

UP and DN signals

UP current and DN current

I have attached the waveforms.

I have also attached the charge pump, vco type is LC. varacator cap is 200fF to 800fF.