EE18

Newbie level 4

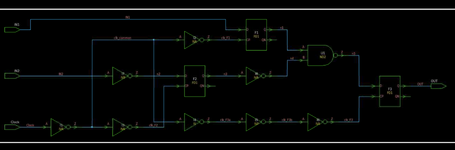

I am simulating the circuit attached with cells from the lsi_10k.lib built-in library (provided with Design Compiler/PrimeTime) and have enforced the constraints below:

Setup analysis output:

As you can see, I do have a set_clock_transition command. Nevertheless, there is zero dependence on the value I provide there (whether 0 or very large). Why is this? I expect delay through the inverters (at least the first one on the path! In the report below this is the I1/Z (IVA) cell delay of 0.49 time units) to slow down, but this is not observed. The lsi_10k.lib library does seem to have enough information about the relevant cells that a delay calculator should compute different delays in different slew rate situations too, I think?#-----------------------------------------------#

# ENFORCE CONSTRAINTS

#-----------------------------------------------#

# Define clock plus its natural latency

create_clock -name CLK -period 10 [get_ports Clock]

set_propagated_clock [get_clocks CLK]

set_clock_uncertainty 1 -hold [get_clocks CLK]

set_clock_uncertainty 1 -setup [get_clocks CLK]

set_clock_latency 1 -source [get_clocks CLK]

set_clock_transition 2 [get_clocks CLK]

set_input_delay -clock CLK 2 [all_inputs]

set_output_delay -clock CLK 2 [all_outputs]

Setup analysis output:

Can anyone set me straight on what I'm missing?****************************************

Report : timing

-path_type full_clock_expanded

-delay_type max

-slack_lesser_than 1000000.00

-max_paths 1

-sort_by slack

Design : MyComp

Version: T-2022.03

Date : Tue Aug 13 21:44:09 2024

****************************************

Startpoint: F3 (rising edge-triggered flip-flop clocked by CLK)

Endpoint: OUT (output port clocked by CLK)

Path Group: CLK

Path Type: max

Point Incr Path

---------------------------------------------------------------

clock CLK (rise edge) 0.00 0.00

clock source latency 1.00 1.00

Clock (in) 0.00 1.00 r

I1/Z (IVA) 0.49 1.49 f

I4/Z (IV) 0.67 2.15 r

I5/Z (IVP) 0.21 2.36 f

I6/Z (IVA) 0.31 2.68 r

F3/CP (FD1) 0.00 2.68 r

F3/Q (FD1) 1.37 4.05 f

OUT (out) 0.00 4.05 f

data arrival time 4.05

clock CLK (rise edge) 10.00 10.00

clock network delay (propagated) 1.00 11.00

clock reconvergence pessimism 0.00 11.00

clock uncertainty -1.00 10.00

output external delay -2.00 8.00

data required time 8.00

---------------------------------------------------------------

data required time 8.00

data arrival time -4.05

---------------------------------------------------------------

slack (MET) 3.95

1