Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

"Pad ring" or "pad frame" usually is understood as the periphery (or circumference) of a chip which contains all the bond pads. It also includes several wide tracks for global power supply nodes as, e.g., gnd! , vdd! , possibly separate ones for analog and digital pwr supplies and/or dedicated ESD nodes. In most cases these wide parallel tracks are designed as rings within the pad ring in order to facilitate short access lengths to these global low-resistive nodes.mona123 said:why do we need pad rings for gnd and vcc? thanks.

Right. Additionally it includes the I/O drivers, ESD structures, and the bond pads.prcken said:i see, pad ring is the wide power supply and ground bus

mona123 said:Thanks erik for the answer but my question was why do we need a ring to connect all pads? is to keep the ground of different parts of the ckts at same potential or something?

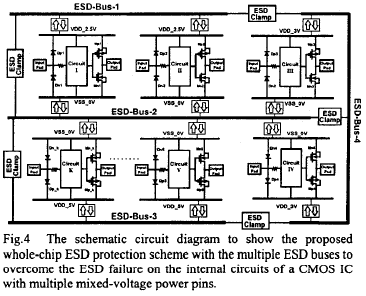

actually that depends, the author used separate ESD buses for better isolation between each blocks at normal working conditions. it need at least two the so called ESD clamps from one block to aonther block. All the ESD buses are floating, they are intended to provide a ESD path for ESD stresses happened between two separate power domains, for example ESD test zapping combination is from VDD1 to VDD2, there are at least two main ESD paths to discharge the large ESD current, i.e VDD1->ESD bus->VDD2 and VDD1->GND1->ESD bus->GND2->VDD21) why do you need separate esd buses. They all must be connected to ground for the discharge, isn't it?

as aforementioned add ESD clamps for better isolation at normal working operation.2) What for are these esd clamps between esd buses? what kind of circuit is there for esd clamps?

the inverters are output buffers, dont necessarily be an inverter there, maybe a source follower, maybe an open drain output, the author just took the inverter for illustration, they are to be protected and can be self-protected, usually the sizes of the inverters are large and layed-out according to ESD rule3) I see CMOS inverters at the pads. How do they help in esd?

no, just make sure not to violate DRCoermens said:you mentioned ~20um as bus width, is there any rule of thumb for spacing between the rings?

there are several ESD paths for ESD current flowing from one pin (VDD1) in respect to another pin(VDD2), at this time ground pin is floating, ESD current is passing through GND bus from one terminal to another.Can you please explain your statement "there are at least two main ESD paths to discharge the large ESD current, i.e VDD1->ESD bus->VDD2 and VDD1->GND1->ESD bus->GND2->VDD2".

when you do ESD Zapmaster testing, you have to define zapping combinations, All pins to GND is just one set of test combinations. All pins to VDD1 is another set of combination, VDD2 to VDD1 zapping is included in this set.How VDD to VDD is discharge path? I am used to thinking that you can only discharge through ground. Also where is GND here ( or may be the picture is small so I can't see?).