X

Xenon02

Guest

Hello !

I've been watching a video about how UART was made from scratch, but I've encountered one problem I couldn't answear.

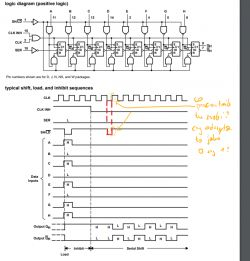

The author of a video :

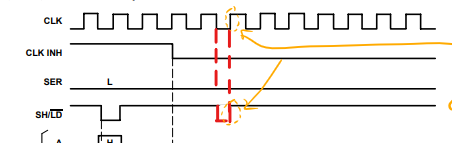

, has used the counter : 74LS165. There was one problem. Because the SHIFT/LOAD bit was changed at the same time as CLK. What do I mean is that the SHIFT/LOAD changed from 0 -> 1 at the same time the clock CLK changed from the 0 -> 1 like in the picture :

What will the D flip flop do ?

Will it still be using asynchronous inputs or shift with synchronous input ?

Because both Load/Shift and CLK are the rising bits.

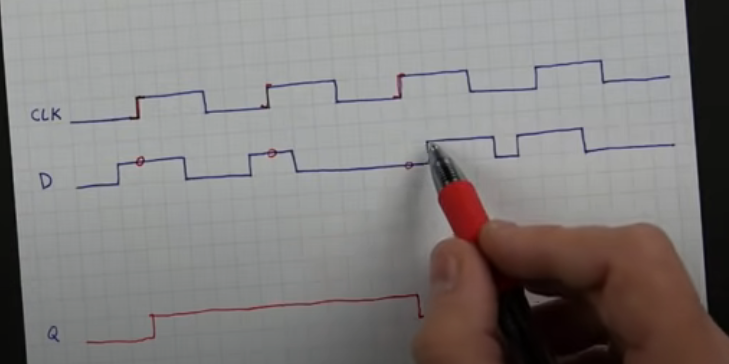

And D flip flop reads during the rising CLK like here :

But in this situation :

Both of them are rising, it is not simple logic level like in the picture with D and CLK (in which D has a certain level).

In author circuit it worked, but I didn't know why when I see SH/LD is a rising bit synchronized with CLK rising bit.

I've been watching a video about how UART was made from scratch, but I've encountered one problem I couldn't answear.

The author of a video :

What will the D flip flop do ?

Will it still be using asynchronous inputs or shift with synchronous input ?

Because both Load/Shift and CLK are the rising bits.

And D flip flop reads during the rising CLK like here :

But in this situation :

Both of them are rising, it is not simple logic level like in the picture with D and CLK (in which D has a certain level).

In author circuit it worked, but I didn't know why when I see SH/LD is a rising bit synchronized with CLK rising bit.