vieha007Electronic

Junior Member level 3

- Joined

- Feb 27, 2011

- Messages

- 25

- Helped

- 3

- Reputation

- 6

- Reaction score

- 1

- Trophy points

- 1,283

- Location

- South Korea

- Activity points

- 1,559

Hi all,

Can you tell me in the design of dc-dc converters (buck, boost), what type of comparator should be used?

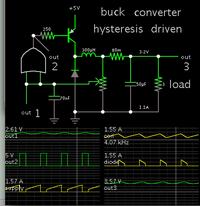

And how about the specification for the comparator? I designed the hystersis comparator for buck converter with the switching frequency is around 1 MHz, however, when I simulate it in the time domain (with one terminal is fed by 10mV sine, and the other at dc), it delays too much.

(Please check the attached images below)

About the opamp, I can designed well with the specification, however, for comparator, I can't imagine clearly what is the spec of comparator, such as delay....

https://obrazki.elektroda.pl/9010683300_1476228003.png

<a title="Comparator2.png" href="http://obrazki.elektroda.pl/9010683300_1476228003.png"><img src="http://obrazki.elektroda.pl/9010683300_1476228003_thumb.jpg" alt="Comparator2.png" /></a>

Any replies from you are really appreciated!

Sincerely,

Can you tell me in the design of dc-dc converters (buck, boost), what type of comparator should be used?

And how about the specification for the comparator? I designed the hystersis comparator for buck converter with the switching frequency is around 1 MHz, however, when I simulate it in the time domain (with one terminal is fed by 10mV sine, and the other at dc), it delays too much.

(Please check the attached images below)

About the opamp, I can designed well with the specification, however, for comparator, I can't imagine clearly what is the spec of comparator, such as delay....

https://obrazki.elektroda.pl/9010683300_1476228003.png

<a title="Comparator2.png" href="http://obrazki.elektroda.pl/9010683300_1476228003.png"><img src="http://obrazki.elektroda.pl/9010683300_1476228003_thumb.jpg" alt="Comparator2.png" /></a>

Any replies from you are really appreciated!

Sincerely,