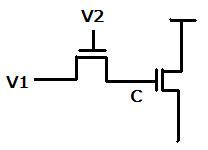

What is the Voltage at Floating node ??

- Thread starter MammPp

- Start date

Similar threads

-

What is the minimum voltage change I can measure with a 6.5-digit multimeter?

- Started by strahd_von_zarovich

- Replies: 14

-

How does an ideal op amp amplify a voltage input when the voltage difference is zero

- Started by newbie_hs

- Replies: 4

-

-

the input reference noise voltage is larger than VDD

- Started by elonjia

- Replies: 3