melkord

Full Member level 3

I want to model Voltage-Controlled Delay in VerilogA using absdelay(target_waveform, delay_control).

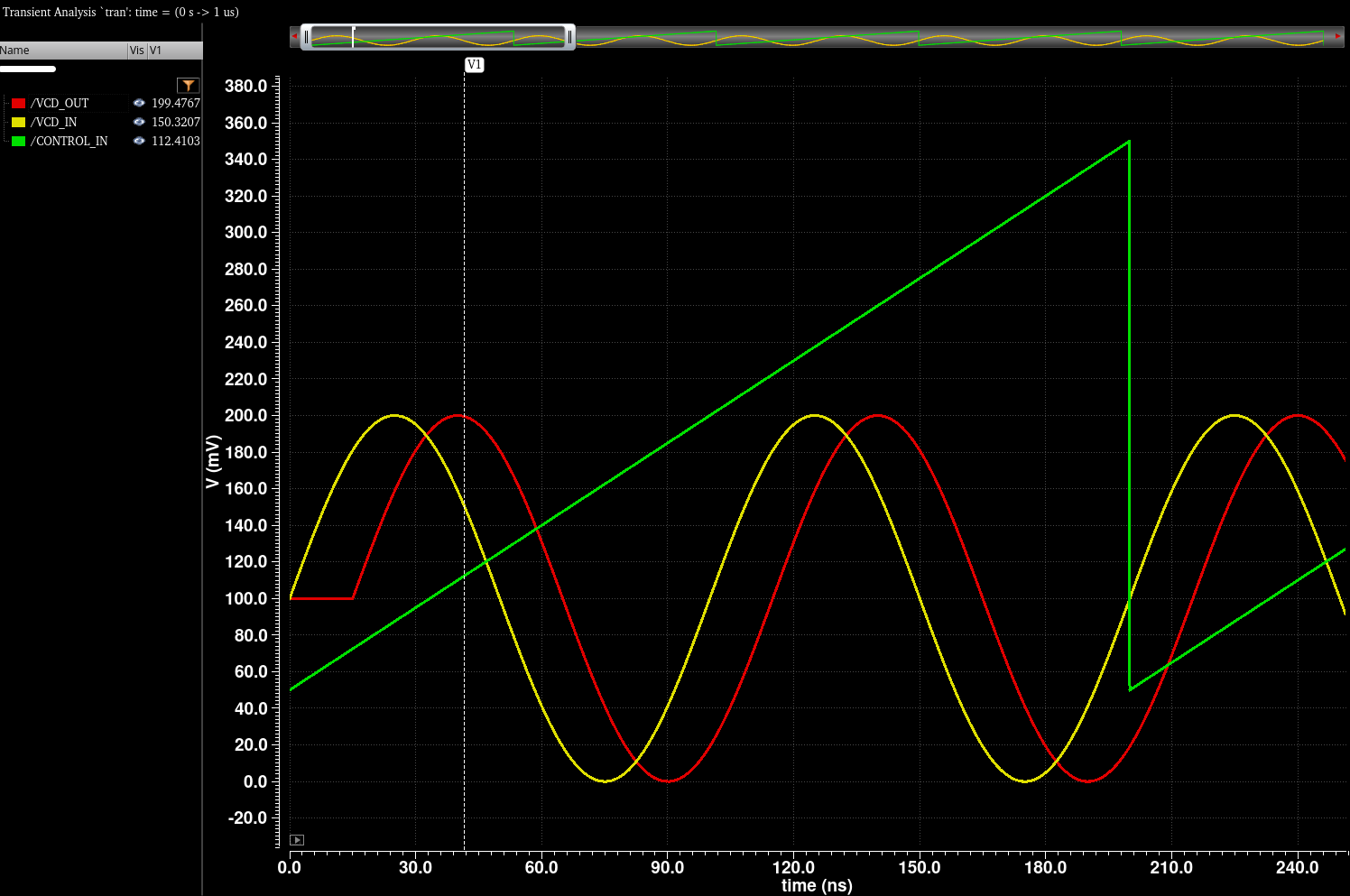

But somehow only the first value of delay_control that is used.

In other words, the delay is there but with fixed value.

Did I miss anything?

Other posts like here and here showed that it should work.

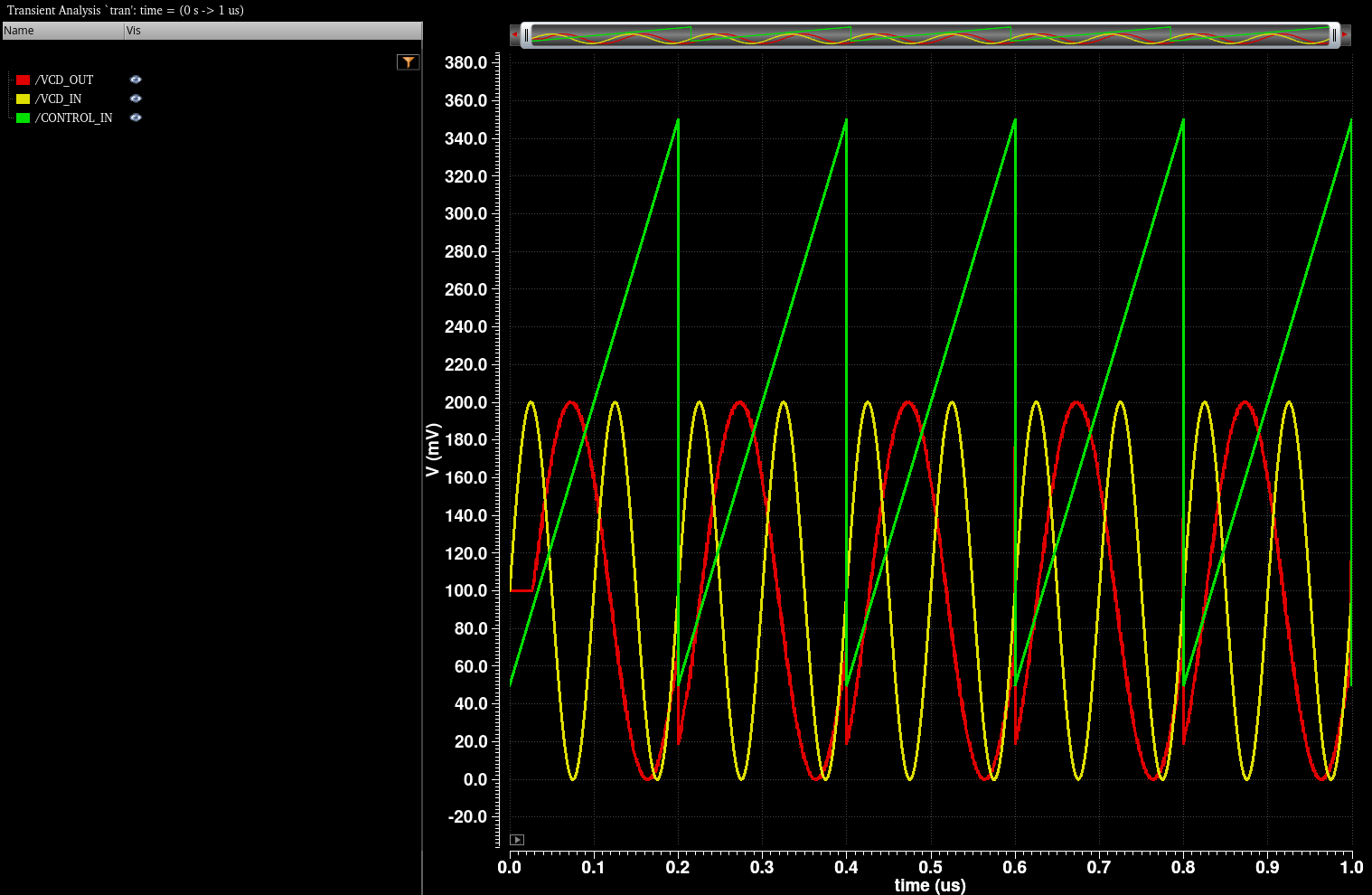

Solved.

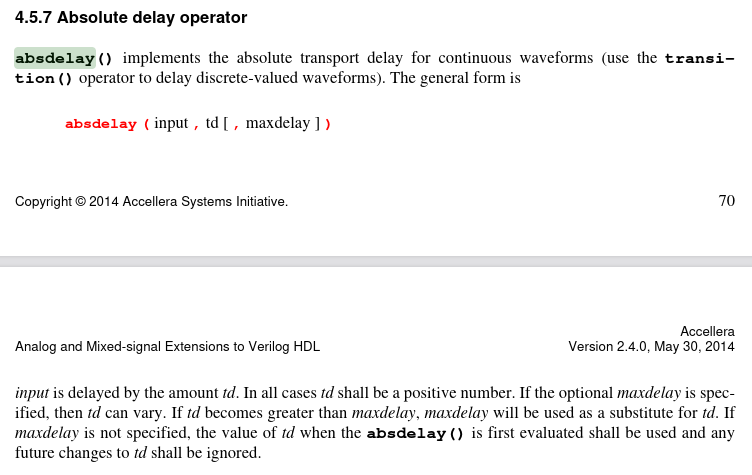

It needs the third argument, i.e., max delay value.

RTFM for me.

But somehow only the first value of delay_control that is used.

In other words, the delay is there but with fixed value.

Did I miss anything?

Code:

// VerilogA for Regulator, voltage_controlled_delay, veriloga

`include "constants.vams"

`include "disciplines.vams"

//`timescale 1ns / 1ps

module voltage_controlled_delay(CONTROL_IN, IN, OUT, ENABLE, VDDA_P1V2, GNDA, VSSA_N1V2);

input CONTROL_IN; electrical CONTROL_IN;

input IN; electrical IN;

output OUT; electrical OUT;

input ENABLE; electrical ENABLE;

input VDDA_P1V2; electrical VDDA_P1V2;

input GNDA; electrical GNDA;

input VSSA_N1V2; electrical VSSA_N1V2;

//integer time_delay;

//parameter real time_delay = 1.0e-9 from (0:inf);

//real time_delay = 7.0e-9;

real v;

real time_delay; // must be positive

analog

begin

time_delay = V(CONTROL_IN)*3e-7;

V(OUT) <+ absdelay(V(IN), time_delay);

end

endmoduleOther posts like here and here showed that it should work.

--- Updated ---

Solved.

It needs the third argument, i.e., max delay value.

RTFM for me.

--- Updated ---

Last edited: