Soh_bhat

Junior Member level 1

Hi there,

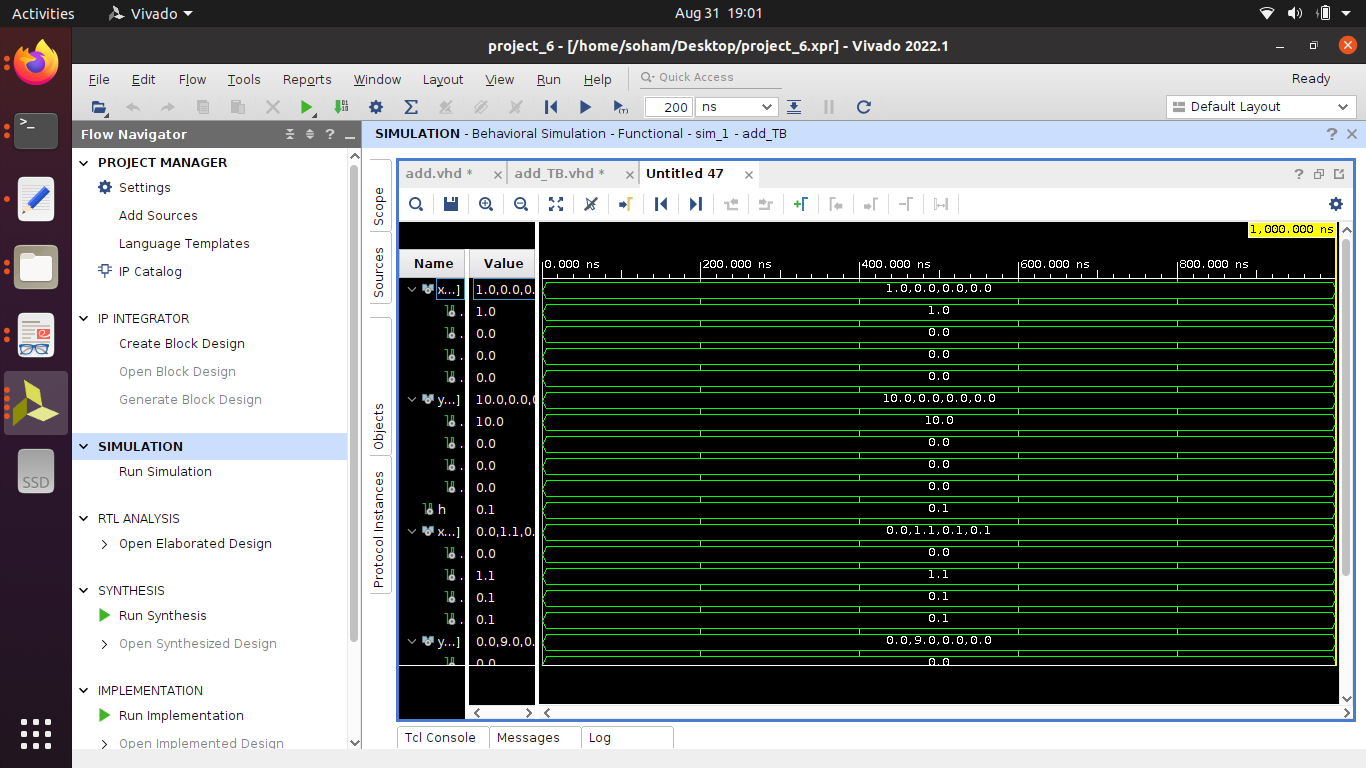

I have tried to add and subtract to check the for loop using two equations. But, whenever I am using it, it is giving result of first step only and the loop is unrolling. What is the error in my code?

It is giving the first output only.

PLease help!!!

I have tried to add and subtract to check the for loop using two equations. But, whenever I am using it, it is giving result of first step only and the loop is unrolling. What is the error in my code?

Code:

Behavioural:

package pk5 is

type T is range 0.0 to 50.0;

type T1 is array (0 to 3) of T;

end pk5;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use work.pk5.all;

entity add is

Port ( x : in T1 ;

y : in T1;

h : in T;

x_o : out T1;

y_o : out T1);

end add;

architecture Behavioral of add is

signal p, q : T1;

begin

process(x, y, h)

begin

x_o(0) <= 0.0;

y_o(0) <= 0.0;

addi: for i in 1 to 3 loop

x_o(i) <= x(i-1) + h;

y_o(i) <= y(i-1) - x(i-1);

end loop;

end Behavioural;

Test Bench:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use work.pk5.all;

entity add_TB is

end add_TB;

architecture Behavioral of add_TB is

component add is

Port ( x : in T1;

y : in T1;

h : in T;

x_o : out T1;

y_o : out T1);

end component;

signal x: T1;

signal y: T1;

signal h: T;

signal x_o: T1;

signal y_o: T1;

begin

uut: add port map (

x => x,

y => y,

h => h,

x_o => x_o,

y_o => y_o);

add_proc: process

begin

x(0) <= 1.0;

y(0) <= 10.0;

h <= 0.1;

wait for 5 ns;

end process;

end Behavioral;It is giving the first output only.

PLease help!!!

Last edited by a moderator: