Vhdlontherise

Newbie

Hi everyone,

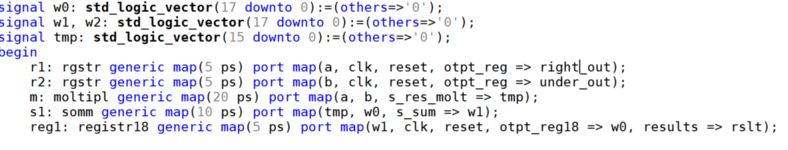

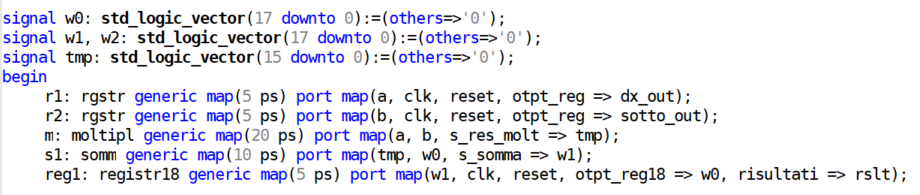

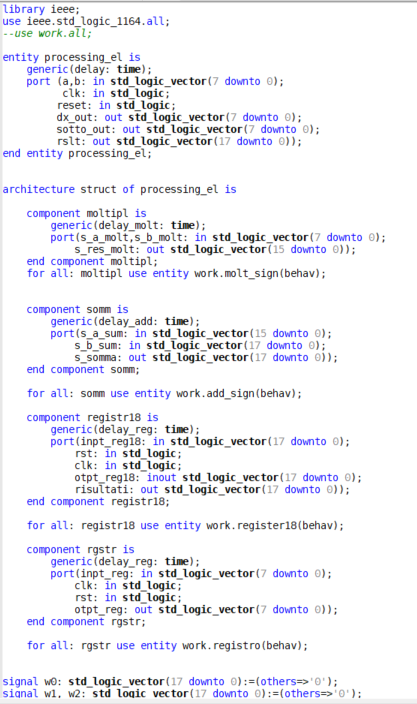

I am facing a problem in writing down my VHDL code.

Basically i have to implement a series of processing elements in order to create a systolic array. These, simplifying the problem, are composed of a multiplier, an adder and a feedback register which has the task of storing the results of the operations and supply them as an input to the adder.

These three elements are implemented with a behavioural architecture while i am trying to implement the processing element with a structural architecture. I am really confused about how to assign the signals in order to send the output of the register as input of the sum.

These are some parts of my code.

I am facing a problem in writing down my VHDL code.

Basically i have to implement a series of processing elements in order to create a systolic array. These, simplifying the problem, are composed of a multiplier, an adder and a feedback register which has the task of storing the results of the operations and supply them as an input to the adder.

These three elements are implemented with a behavioural architecture while i am trying to implement the processing element with a structural architecture. I am really confused about how to assign the signals in order to send the output of the register as input of the sum.

These are some parts of my code.