hawluchapikaa

Newbie

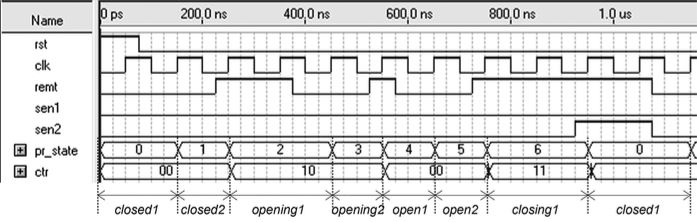

A VHDL design code for a remote-controlled garage door opener with sensors is provided to us. It has 8 states, 4 for each door. Testbench is not provided, and I did one (with help of testbench generator as well). The output should look something like this:

I used web application called EDA Playground for simulation. Below is the link of it:

Kinda new to this. Don't know why it doesn't run.

Is there supposed to be a proper sequence of inputs for this specific code or am I missing some other inputs, such as those in testbench stimuli?

Hope someone could help analyzing the design and what I should put in the testbench stimuli cause

I think I'm missing something.

[MODERATOR ACTION]

Embedded code to the thread

Design

Testbench

I used web application called EDA Playground for simulation. Below is the link of it:

Kinda new to this. Don't know why it doesn't run.

Is there supposed to be a proper sequence of inputs for this specific code or am I missing some other inputs, such as those in testbench stimuli?

Hope someone could help analyzing the design and what I should put in the testbench stimuli cause

I think I'm missing something.

[MODERATOR ACTION]

Embedded code to the thread

Design

Code:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity garage_door_controller is

port (

remt, sen1, sen2, clk, rst : in std_logic;

ctr : out std_logic_vector (1 downto 0)

);

end entity;

architecture moore_fsm of garage_door_controller is

type state is (closed1, closed2, opening1, opening2, open1, open2, closing1, closing2);

signal pr_state, nx_state : state;

begin

process (clk, rst)

begin

if rst = '1' then

pr_state <= closed1;

elsif rising_edge(clk) then

pr_state <= nx_state;

end if;

end process;

process (pr_state, remt, sen1, sen2)

begin

case pr_state is

when closed1 => ctr <= "00";

if remt = '0' then

nx_state <= closed2;

else

nx_state <= closed1;

end if;

when closed2 => ctr <= "00";

if remt = '1' then

nx_state <= opening1;

else

nx_state <= closed2;

end if;

when opening1 => ctr <= "10";

if sen1 = '1' then

nx_state <= open1;

elsif remt = '0' then

nx_state <= opening2;

else

nx_state <= opening1;

end if;

when opening2 => ctr <= "10";

if remt = '1' or sen1 = '1' then

nx_state <= open1;

else

nx_state <= opening2;

end if;

when open1 => ctr <= "00";

if remt = '0' then

nx_state <= open2;

else

nx_state <= open1;

end if;

when open2 => ctr <= "00";

if remt = '1' then

nx_state <= closing1;

else

nx_state <= open2;

end if;

when closing1 => ctr <= "11";

if sen2 = '1' then

nx_state <= closed1;

elsif remt = '0' then

nx_state <= closing2;

else

nx_state <= closing1;

end if;

when closing2 => ctr <= "11";

if remt = '1' or sen2 = '1' then

nx_state <= closed1;

else

nx_state <= closing2;

end if;

end case;

end process;

end architecture;Testbench

Code:

library ieee;

use ieee.std_logic_1164.all;

entity tb_garage_door_controller is

end tb_garage_door_controller;

architecture tb of tb_garage_door_controller is

component garage_door_controller

port (remt : in std_logic;

sen1 : in std_logic;

sen2 : in std_logic;

clk : in std_logic;

rst : in std_logic;

ctr : out std_logic_vector (1 downto 0)

);

end component;

signal remt : std_logic;

signal sen1 : std_logic;

signal sen2 : std_logic;

signal clk : std_logic;

signal rst : std_logic;

signal ctr : std_logic_vector (1 downto 0);

constant clk_period : time := 10 ns;

begin

dut : garage_door_controller

port map (remt => remt,

sen1 => sen1,

sen2 => sen2,

clk => clk,

rst => rst,

ctr => ctr

);

clk_process :process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

stimuli : process

begin

remt <= '0';

sen1 <= '0';

sen2 <= '0';

rst <= '1';

wait for clk_period*10;

rst <= '0';

wait for clk_period*10;

remt <= '0';

wait for clk_period*10;

remt <= '1';

wait for clk_period*10;

sen1 <= '1';

wait for clk_period*10;

sen2 <= '1';

wait for clk_period*10;

remt <= '1';

wait for clk_period*10;

remt <= '1';

wait for clk_period*10;

wait;

end process;

end tb;

configuration cfg_tb_garage_door_controller of tb_garage_door_controller is

for tb

end for;

end cfg_tb_garage_door_controller;

Last edited by a moderator: