dirac16

Member level 5

I tried to simulate the following Verilog code by AMS simulator:

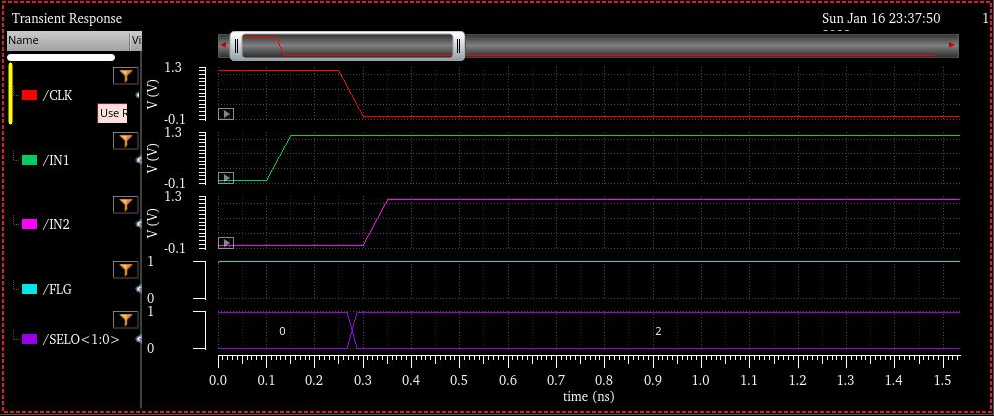

Here's the output for the input test signals shown ( i1 : IN1, i2 : IN2, clk : CLK, flg : FLG and sel : SELO)

The output registers SELO<1:0> and FLG just before the falling edge of CLK are 0 and 1, respectively. That is not what I expect because before a falling transition occurs on CLK, the statements inside the always block are not executed, so neither FLG nor SELO<1:0> should have certain values before CLK's falling transition (Rather they must be evaluated to x). What's wrong? It's like the always block is executed at time 0. I changed negedge to posedge and ran the same simulation with CLK changed to a rising edge type. This time the outputs were evaluated to x before CLK's rising transition. So not sure why the code does not work for negedge.

Code:

module test(i1,i2,clk,sel,flag);

input i1, i2;

input clk;

output reg [1:0] sel;

output reg flag;

always @(negedge clk) begin

sel[1] <= i1;

sel[0] <= i2;

flag <= 1;

end

endmoduleHere's the output for the input test signals shown ( i1 : IN1, i2 : IN2, clk : CLK, flg : FLG and sel : SELO)

Last edited: