sabu31

Advanced Member level 1

Hi,

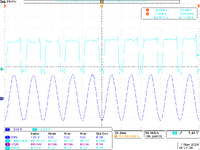

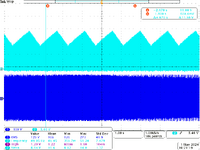

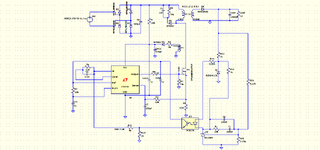

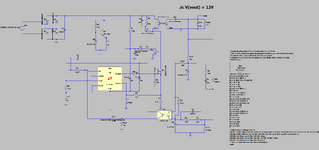

I am making a 12V supply using UC3842. The charging resistor is 50k. However, as I increase the input AC voltage, the Vcc Voltage is fluctuation. What could be the issue?

The converter is a flyback configuration with output at 12V and 12W.

I am making a 12V supply using UC3842. The charging resistor is 50k. However, as I increase the input AC voltage, the Vcc Voltage is fluctuation. What could be the issue?

The converter is a flyback configuration with output at 12V and 12W.