danny davis

Banned

The solid state relay is powered by 120 volts AC , the signal of the solid state relay goes direct a controller PIN

What does the solid state relay do?

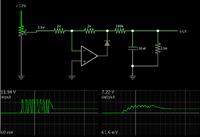

Op-Amp Detector, What does it do ? for logic circuits? it takes an input signal and does what?

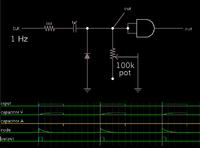

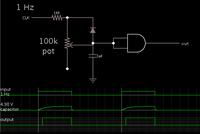

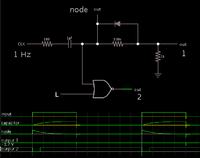

Here is an RC network in the feedback section of an op-amp , what does it do?

This IC voltage Detector, goes direct to the Micro-controllers RESET pin, what does the IC voltage detector do? once the VCC is to low it Resets the Micro-controller?

If there is a short and the VCC is low all the time , it's just going to keep Resetting the Microcontroller right?

What does these LF13333N Switches do?

When they have an square waveform on the input pin of a LF13333N the output of the LF13333N switch changes the Amplitude of the square waveform i have noticed

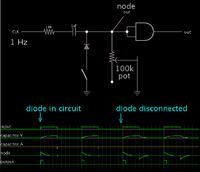

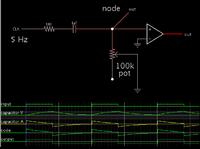

What does the Diodes do? The Nor gates have these Diodes for what?

What does the solid state relay do?

Op-Amp Detector, What does it do ? for logic circuits? it takes an input signal and does what?

Here is an RC network in the feedback section of an op-amp , what does it do?

This IC voltage Detector, goes direct to the Micro-controllers RESET pin, what does the IC voltage detector do? once the VCC is to low it Resets the Micro-controller?

If there is a short and the VCC is low all the time , it's just going to keep Resetting the Microcontroller right?

What does these LF13333N Switches do?

When they have an square waveform on the input pin of a LF13333N the output of the LF13333N switch changes the Amplitude of the square waveform i have noticed

What does the Diodes do? The Nor gates have these Diodes for what?