Faizan shafi

Newbie level 6

I am designing a v band lna . I have done the dc biasing and the s parameter simulation.

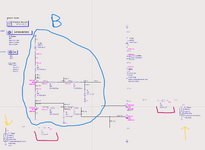

I have shared the schematic below. The blue circle has my biasing network. the yellow arrows point to input nd output ports. red indicates the blocking capacitors.

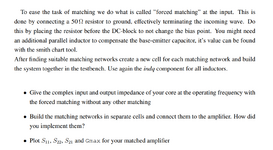

I am following a tutorial , and i have shared a section of it below.

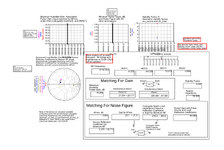

I have found my input impedance which is 9.690 -25.092j.

I am really confused about the forced matching part. Where should I connect this 50 ohm resistor? In my main schematic or when i open my Smith chart tool and plug in zs and zin and then in the middle of these two should I put my 50 oh resistor.

Will this blocking capacitor be a part of my matching network or will i simply remove it after making the matching network.

can someone please explain me the steps of how should i move forward. Thank you.

I have shared the schematic below. The blue circle has my biasing network. the yellow arrows point to input nd output ports. red indicates the blocking capacitors.

I am following a tutorial , and i have shared a section of it below.

I have found my input impedance which is 9.690 -25.092j.

I am really confused about the forced matching part. Where should I connect this 50 ohm resistor? In my main schematic or when i open my Smith chart tool and plug in zs and zin and then in the middle of these two should I put my 50 oh resistor.

Will this blocking capacitor be a part of my matching network or will i simply remove it after making the matching network.

can someone please explain me the steps of how should i move forward. Thank you.