zuirgham

Junior Member level 3

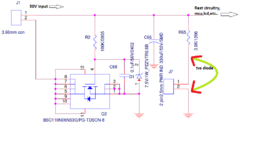

refer to fig1.

at j7 Connector, 12v LED(Part Number: 5110F1-12V) is connected. This LED is directly exposed to the outside world from the casing. when we do ESD testing at the LED spot,

case1: @ +-8KV, we are facing no issues.

case 2: @ +-15KV, the rest circuitry, mcu, lcd is going for a restart.

I was suspecting a voltage dip at the line, so i thought of using an ESD diode near to LED. I used this TVS diode (Part Number:SMBJ33CA) at the j7 Junction, and was still seeing the circuitry going for a reset, LCD was switching ON, oFF etc.

from a mechanical perspective, i was thinking of using an external glass casing atop LED, could there be any improvements in the circuit so as to withstand high KV ESD, or are there any more suggestions i can follow up before going for the next test

at j7 Connector, 12v LED(Part Number: 5110F1-12V) is connected. This LED is directly exposed to the outside world from the casing. when we do ESD testing at the LED spot,

case1: @ +-8KV, we are facing no issues.

case 2: @ +-15KV, the rest circuitry, mcu, lcd is going for a restart.

I was suspecting a voltage dip at the line, so i thought of using an ESD diode near to LED. I used this TVS diode (Part Number:SMBJ33CA) at the j7 Junction, and was still seeing the circuitry going for a reset, LCD was switching ON, oFF etc.

from a mechanical perspective, i was thinking of using an external glass casing atop LED, could there be any improvements in the circuit so as to withstand high KV ESD, or are there any more suggestions i can follow up before going for the next test