sunli567

Junior Member level 1

I am designing an two-stage opamp.

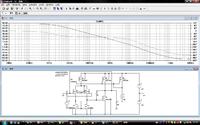

Following one is my circuit.

I use this equation to calculate the DC gain, which is 3227(714db).

gm5(rds5//rds1)gm3(rds3//rds7)

But the simulation result given by LTspic is 76.4db, about 6606 times.

why is it so large? but the other parameter is nearly the same as the ones calculated.

pls help me!

thanks!

Following one is my circuit.

I use this equation to calculate the DC gain, which is 3227(714db).

gm5(rds5//rds1)gm3(rds3//rds7)

But the simulation result given by LTspic is 76.4db, about 6606 times.

why is it so large? but the other parameter is nearly the same as the ones calculated.

pls help me!

thanks!