Soh_bhat

Junior Member level 1

Hi there,

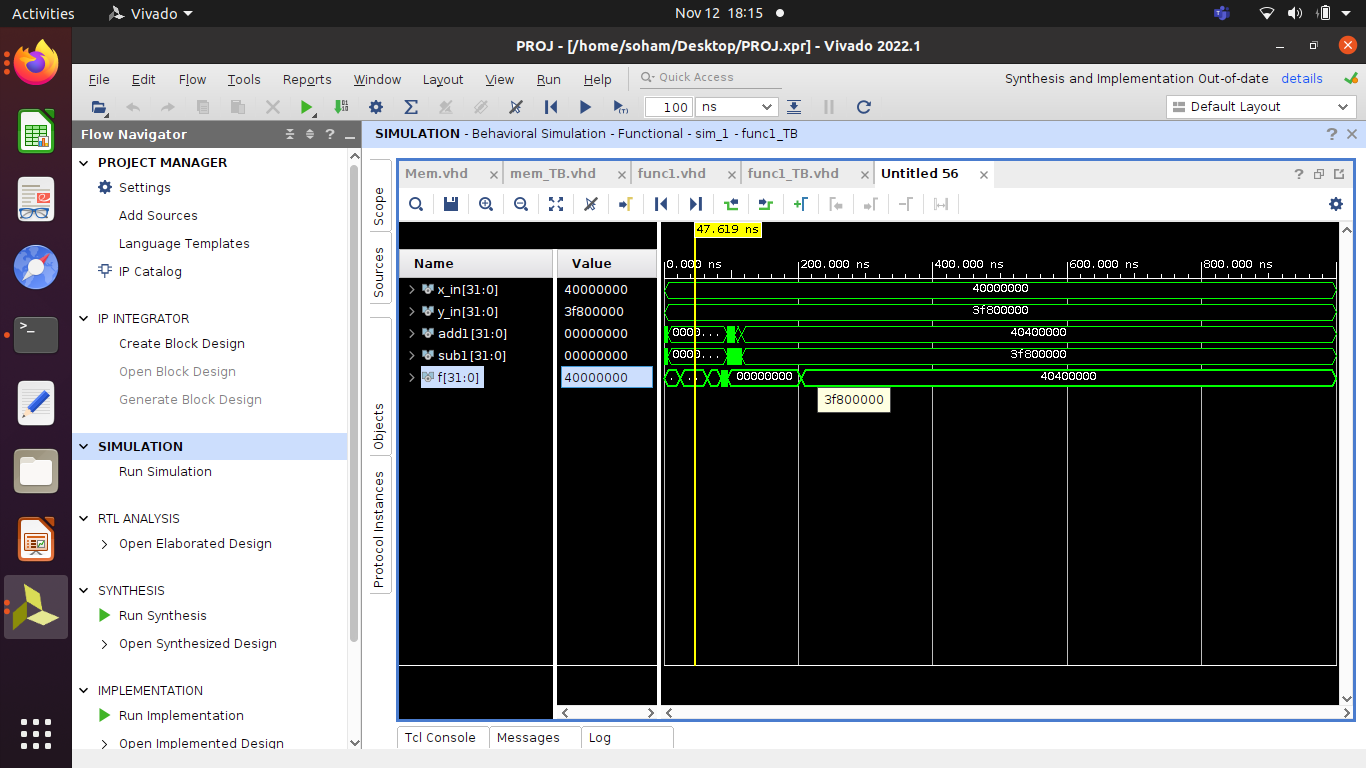

Good day. I am doing a simple mathematical operation using VIvado IP Floating point core. Also, I am getting the result. But as you can see, before getting the result, I am getting some unwanted values in the add & sub section. According to the operation, I will get 40400000 in the final result which is showing the waveform. But there are some unwanted values beforehand. Could you please tell me why this is so?

Thanks in advance.

Good day. I am doing a simple mathematical operation using VIvado IP Floating point core. Also, I am getting the result. But as you can see, before getting the result, I am getting some unwanted values in the add & sub section. According to the operation, I will get 40400000 in the final result which is showing the waveform. But there are some unwanted values beforehand. Could you please tell me why this is so?

Thanks in advance.