sarjumaharaj

Junior Member level 1

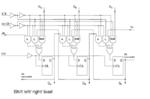

Have a look at the image i have attached. It is an example of universal shift register. It was in one of the sections of parallel in parellel out universal shift register. However, I think that this USR can do serial input as well with it's SR and SL inputs. Can anyone please see and tell me.

Have a look at the image i have attached. It is an example of universal shift register. It was in one of the sections of parallel in parellel out universal shift register. However, I think that this USR can do serial input as well with it's SR and SL inputs. Can anyone please see and tell me.Also, for the load and gate, one of the port is connected to the rightshift on signal LR. Is it important that we do that, or is it necessary at all?