yefj

Advanced Member level 5

- Joined

- Sep 12, 2019

- Messages

- 1,526

- Helped

- 1

- Reputation

- 2

- Reaction score

- 5

- Trophy points

- 38

- Activity points

- 9,173

Hello , I have an intresting phenomena when I am trying to lock my PLL by the system shown below.

My error voltage which is IF of a mixer gets amplified and the amplified signal goes into YIG(VCO)

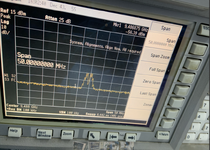

When the phase difference voltage is low and rippling as shown in photo 1, then I see the VCO going crazy back and forth changing the frequency as shown in photo 2.

However when I turn the phase shifter and the error voltage is getting higher then I get straight line error shape and a single tone.

I wonder about two things :

1.When I put big phase shift then IF signal voltage also is high.

High IF signal goes into my amplifier and its getting comppressed (final amount of current going into YIG)

So thats in turn creates a final amount of shift in the VCO so thats why i get a single tone.

But error signal after the feedback is a straight line.

What is the meaning of that?

2. My VCO needs to be connected as negative feedback.

Does it act like the feedback is negative in my system?

Thanks.

My error voltage which is IF of a mixer gets amplified and the amplified signal goes into YIG(VCO)

When the phase difference voltage is low and rippling as shown in photo 1, then I see the VCO going crazy back and forth changing the frequency as shown in photo 2.

However when I turn the phase shifter and the error voltage is getting higher then I get straight line error shape and a single tone.

I wonder about two things :

1.When I put big phase shift then IF signal voltage also is high.

High IF signal goes into my amplifier and its getting comppressed (final amount of current going into YIG)

So thats in turn creates a final amount of shift in the VCO so thats why i get a single tone.

But error signal after the feedback is a straight line.

What is the meaning of that?

2. My VCO needs to be connected as negative feedback.

Does it act like the feedback is negative in my system?

Thanks.

Attachments

Last edited by a moderator: