Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

The simplified schematic doesn't show the input bias, I assume there can be a DC offset if required. If so, it doesn't really matter if the FET is enhancement or depletion mode type, the bias polarity and level can be adjusted according to intended operation mode. It could be even class F rather than C with a very small duty cycle.For proper biasing: The circuit requires a source resistor bypassed with a capacitor to obtain self-bias.

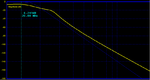

It's not so that class C matching networks are generally omitting this capacitor, but it may appropriate under circumstances.1. Why in the filter missing capacitor between C4 and L3, illustratively drawn in red ?

Real value in LPF not quite fit me with assumptions.

How do you determine "RF2"?I thing source impedance is Inductance RF2 + Capacitance Xc4 + serial resistance C4

No. Both networks are designed for 50 Ohms interface impedance. The can be connected without changing them. Of course C1 and C2 can be combined into one capacitor.I think here must be used LPF where have on first position only L. Am I right?

100nF NP0 isn't feasible. No problem to use X7R, but need to check current rating related to ESR.Is good choice for 30m frequency and 30W Power SMD ceramic NP0 100nF and voltage rating 4x Vdd?

No. Both networks are designed for 50 Ohms interface impedance. The can be connected without changing them. Of course C1 and C2 can be combined into one capacitor.