james.qiu

Newbie level 6

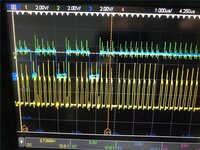

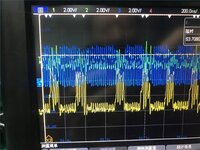

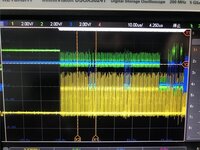

Hello , when i use TXS0104E , B port is 5V signal, A port is 3.3V, signal is SWD data with 10k external pull up resistor , the problem is when try to connect the j-link with 4Mhz,the data signal (port B)is clamping to 3,3V, then oscillation ,finally clamping to 2V at low voltage. i also try the nxp NTS0104PW , it is no problem, jlink work normally.

one assumption is TXS0104E with more high port capactor than NTS0104PW

could you help check it ?

one assumption is TXS0104E with more high port capactor than NTS0104PW

could you help check it ?