metamisers

Junior Member level 2

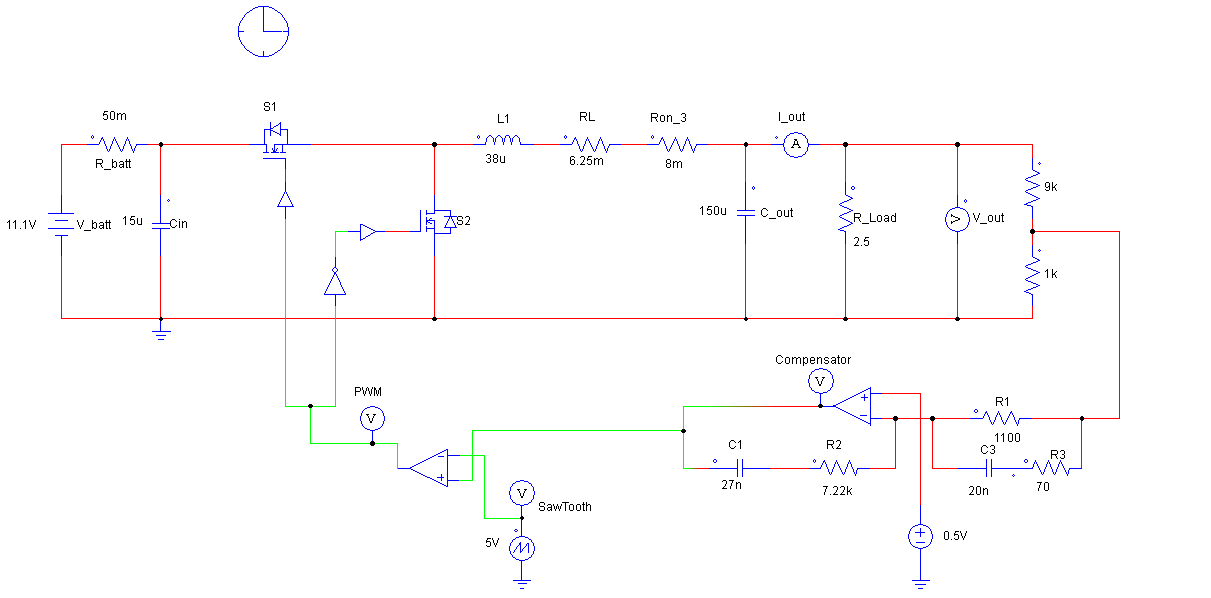

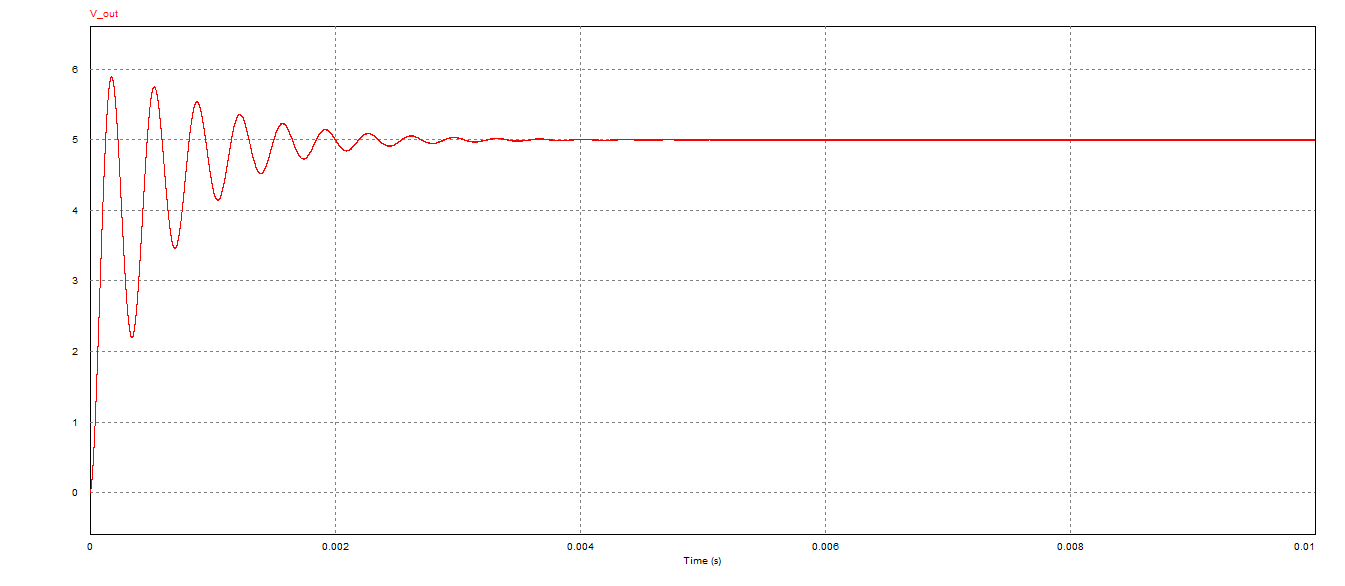

I am having trouble in tuning the PID control loop of the synchronous Buck converter. Figure 1 shows the circuit and figure 2 shows the response. I want the output voltage at 5V without any ringing and settling time is not important for me, however I am unable to tune this damn controller circuit

Figure 1.

Figure 2.

Also attached is the PSIM 9 file for this circuit. I used the K factor method to design the controller but proper could not damp the resonances properly. Any help and any guidance will be highly appreciated.

Thank you.

Figure 1.

Figure 2.

Also attached is the PSIM 9 file for this circuit. I used the K factor method to design the controller but proper could not damp the resonances properly. Any help and any guidance will be highly appreciated.

Thank you.