areddon

Newbie level 4

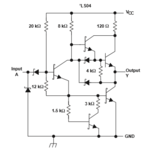

In a prototype board for Lithium battery charge control, I have a three input AND gate (74LS11N).

The inputs to the AND gate are:

1A = 5/0 volts from a digital output pin on an Arduino nano

1B = drain of an N-channel MOSFET (HUF76423P3) acting as low side switch on a 5 volt supply

1C = drain of a P=channel MOSFET (STP10P6F6) acting as a high side switch on a 5 volt supply

The output from AND gate (1Y) goes to the gate of another N-channel MOSFET (HUF76423P3) which acts as a low side switch on the 12 volt control signal to a solid state relay.

In testing the prototype, the gate is not working as expected. Upon removal and testing (tried twice) I found the AND gates had one input pin that did not affect the state of the output

I did not take great care against ESD so it is possible that i damaged the AND gate during assembly, BUT before trying a third time with proper ESD protection, I would like to know:

a) Is there something obvious in this circuit that could be frying the AND gate?

b) Is the LS gate appropriate or would a HC gate be better?

The inputs to the AND gate are:

1A = 5/0 volts from a digital output pin on an Arduino nano

1B = drain of an N-channel MOSFET (HUF76423P3) acting as low side switch on a 5 volt supply

1C = drain of a P=channel MOSFET (STP10P6F6) acting as a high side switch on a 5 volt supply

The output from AND gate (1Y) goes to the gate of another N-channel MOSFET (HUF76423P3) which acts as a low side switch on the 12 volt control signal to a solid state relay.

In testing the prototype, the gate is not working as expected. Upon removal and testing (tried twice) I found the AND gates had one input pin that did not affect the state of the output

I did not take great care against ESD so it is possible that i damaged the AND gate during assembly, BUT before trying a third time with proper ESD protection, I would like to know:

a) Is there something obvious in this circuit that could be frying the AND gate?

b) Is the LS gate appropriate or would a HC gate be better?