viperpaki007

Full Member level 5

Hi,

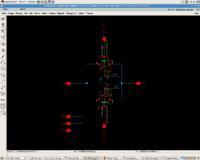

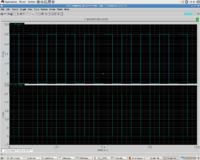

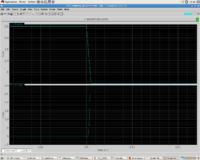

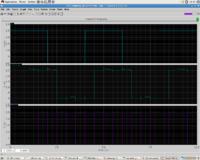

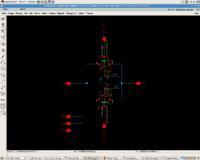

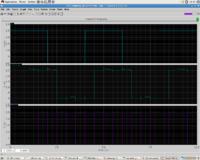

I am simulating Transmission gate D flip flop in cadence but my simulation results show glitches at output. I am attaching my circuit diagram below. Can somebody suggest what is the problem

simulation: Transient

step size 0.1ns

Max step 0.1ns

Input frequency 250kHz

clock frequency 1MHz

- - - Updated - - -

I am also attaching my transmission gate circuit

I am simulating Transmission gate D flip flop in cadence but my simulation results show glitches at output. I am attaching my circuit diagram below. Can somebody suggest what is the problem

simulation: Transient

step size 0.1ns

Max step 0.1ns

Input frequency 250kHz

clock frequency 1MHz

- - - Updated - - -

I am also attaching my transmission gate circuit