r1caw ex ua6bqg

Member level 2

Hi all!

I have a question about translation step during logic synthesis. For example, I have RTL description of the multiplier (assign C=A*B).

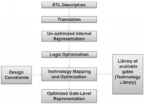

During translation step logic synthesis tool will convert my multiplier RTL into general unoptimized netlist and then optimize it (during optimization stage using constraints) and map it (during mapping step using target libraries).

The question is how translator choose realization of the multiplier at the gate-level (there are a lot of them at the gate-level)?

Is it correct that during translation step EDA tool will recognize my RTL as multiplier and translate it into "abstract black-box multiplier" and only during optimization step convert it into desired gate-level multiplier realization?

I have a question about translation step during logic synthesis. For example, I have RTL description of the multiplier (assign C=A*B).

During translation step logic synthesis tool will convert my multiplier RTL into general unoptimized netlist and then optimize it (during optimization stage using constraints) and map it (during mapping step using target libraries).

The question is how translator choose realization of the multiplier at the gate-level (there are a lot of them at the gate-level)?

Is it correct that during translation step EDA tool will recognize my RTL as multiplier and translate it into "abstract black-box multiplier" and only during optimization step convert it into desired gate-level multiplier realization?