matrixofdynamism

Advanced Member level 2

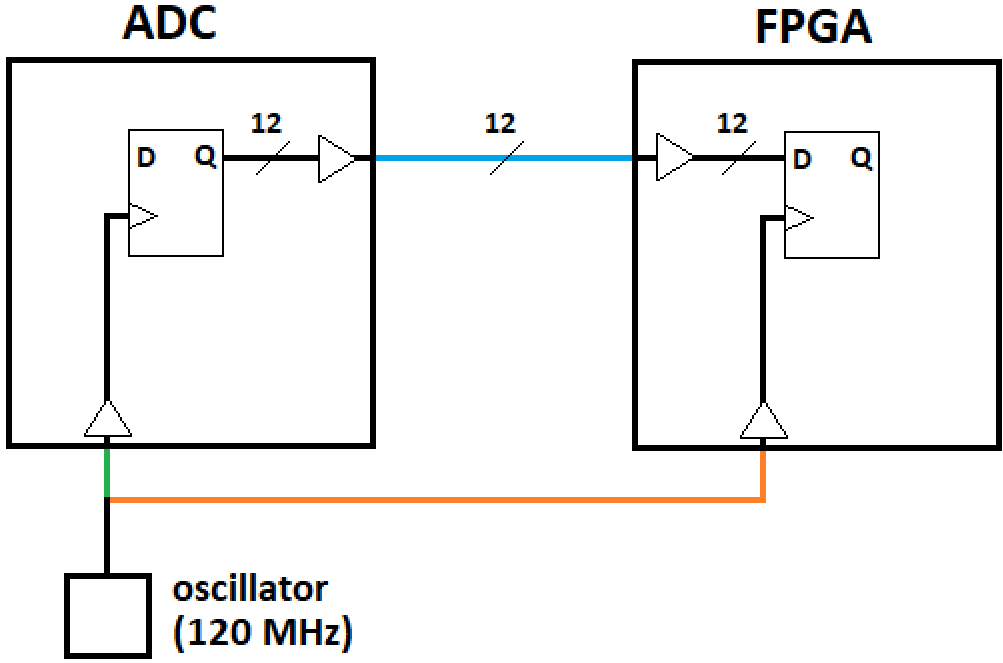

An ADC uses 12 single ended CMOS signals to transfer data to an FPGA. Both of them share 120 MHz source on the PCB. However, the PCB delay from the oscillator to the clock pin of each component is different. Here is the conceptual diagram where the PCB tracks are color coded. There are 12 PCB tracks for the data since the data is transferred parallely.

I have no clue how to constrain these 12 timing paths. They all involve delay on PCB tracks. How should the user constrain these paths using SDC commands? I think that I need to use some sort of add min delay, add max delay e.t.c in some way.

I have no clue how to constrain these 12 timing paths. They all involve delay on PCB tracks. How should the user constrain these paths using SDC commands? I think that I need to use some sort of add min delay, add max delay e.t.c in some way.