engr_joni_ee

Advanced Member level 3

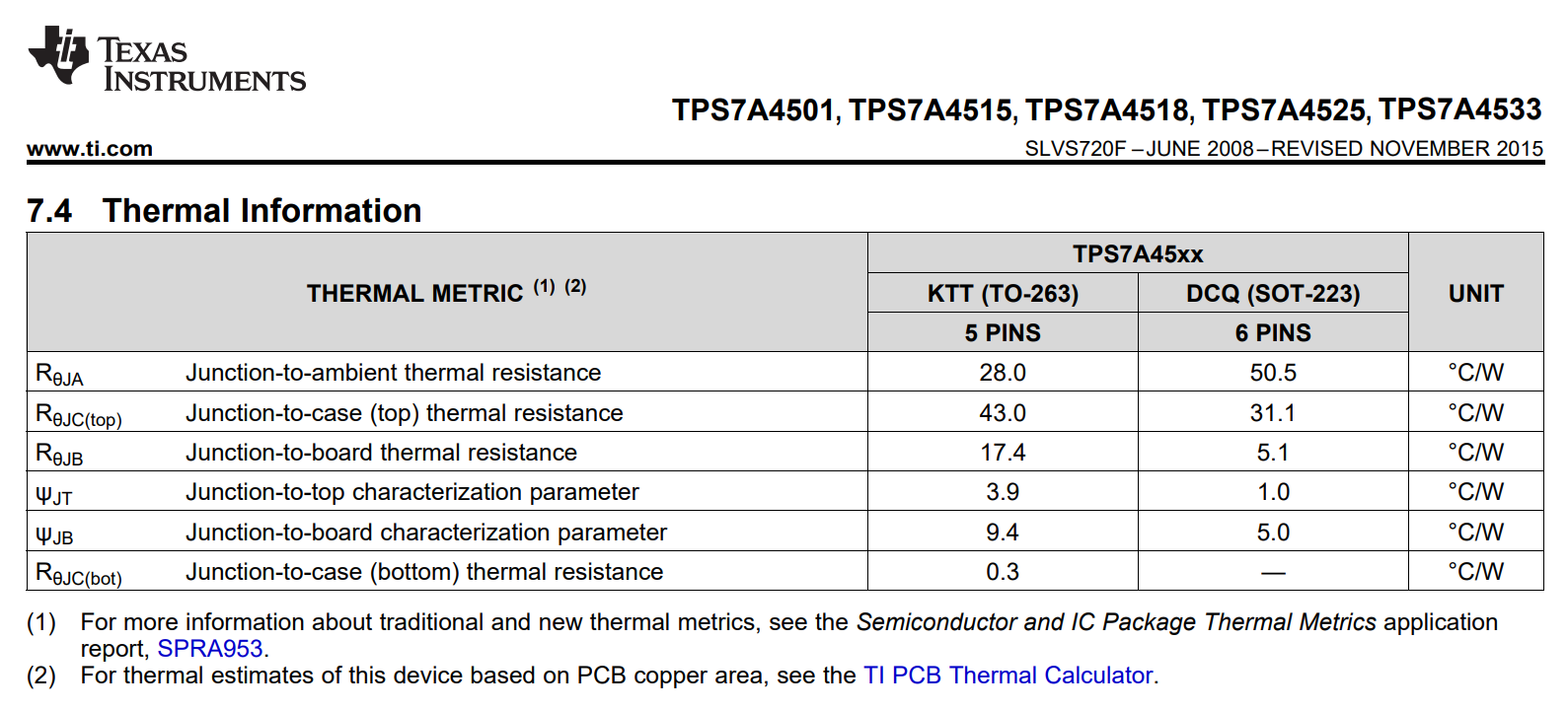

I have found in a LDO voltage regulator the following information.

Junction-to-ambient thermal resistance = 28 degC

Junction-to-case (top) thermal resistance = 43 degC

This look like strange to me. How the junction-to-ambient is lower then the junction-to-case (top) thermal resistance ?

Junction-to-ambient thermal resistance = 28 degC

Junction-to-case (top) thermal resistance = 43 degC

This look like strange to me. How the junction-to-ambient is lower then the junction-to-case (top) thermal resistance ?