EDA_hg81

Advanced Member level 2

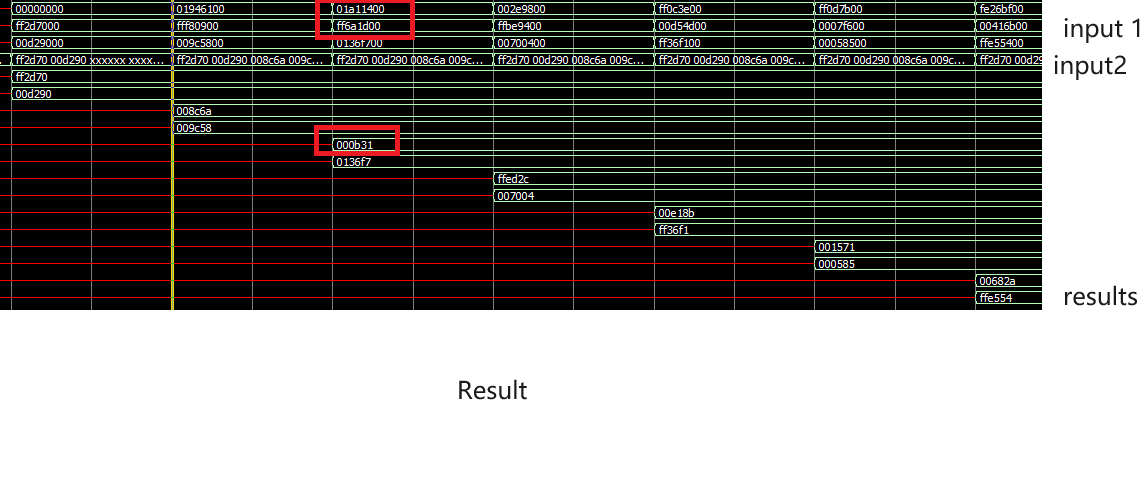

I am using Microchip Libero SOC to process the incoming data using Verilog.

But I found out the Verilog signed math operation is not correct, such as "01a114" + "ff6a1d" should = 010b31, but the result is "000b31"

Please let me know how to fix this problem.

Many thanks in advance.

But I found out the Verilog signed math operation is not correct, such as "01a114" + "ff6a1d" should = 010b31, but the result is "000b31"

Please let me know how to fix this problem.

Many thanks in advance.