yefj

Advanced Member level 4

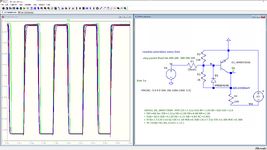

Hello,I have attached two LTSPICE files.There are two kinds of plots,saturated and non saturated shown below.

I dont understand where is the significant delay in the signal in the saturated state.

How can i see that there is stretch in the non saturated PNP?

Saturated PNP

NON Saturated

I dont understand where is the significant delay in the signal in the saturated state.

How can i see that there is stretch in the non saturated PNP?

Saturated PNP

NON Saturated