Sergoi

Newbie

- Joined

- Jan 27, 2022

- Messages

- 4

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Location

- Catania, Italy

- Activity points

- 139

Hi folks.

I have single port memory with a dedicated test clock port, i.e. in *.lvlib for clock port:

there are also select for CLK/TCLK in *.lvlib

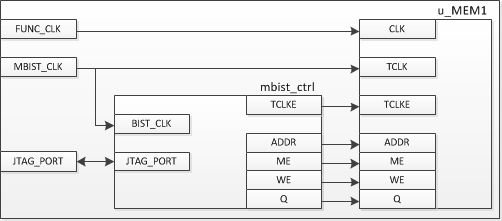

Moreover, separate test clock port (MBIST_CLK) must be present in design, i.e. it is impossible to use functional clock(FUNC_CLK) for mbist. Required mbist config is like this (without memory interfaces/collars for simplicity):

I'm using tshell, not LV. So, i'm add_clock to 'TCLK' and add_dft_clock_mux for 'CLK' 'TCLK' with 'all_test' as a dft control signal. But at the check_design_rule stage i have a DFT_C1-1 error "Memory clock not properly sourced by a declared clock". Aslo i'v tried to use add_dft_control_points and other ways, like add single pseudo port for both CLK and TCLK, to solve this problem, but it's all fails, DFT_C1-1 error staying.

Does anyone knows how to use separate test mbist clock for testing memories with internal mux on clock port?

I have single port memory with a dedicated test clock port, i.e. in *.lvlib for clock port:

Code:

Port (CLK)

{

Direction: INPUT;

Function: Clock;

Plarity: ActiveHigh;

EmbeddedTestLogic {

TestInput: TCLK;

}

}

Code:

Port (TCLKE)

{

Direction: INPUT;

Polarity: ActigeHigh;

Function: BistEn;

}Moreover, separate test clock port (MBIST_CLK) must be present in design, i.e. it is impossible to use functional clock(FUNC_CLK) for mbist. Required mbist config is like this (without memory interfaces/collars for simplicity):

I'm using tshell, not LV. So, i'm add_clock to 'TCLK' and add_dft_clock_mux for 'CLK' 'TCLK' with 'all_test' as a dft control signal. But at the check_design_rule stage i have a DFT_C1-1 error "Memory clock not properly sourced by a declared clock". Aslo i'v tried to use add_dft_control_points and other ways, like add single pseudo port for both CLK and TCLK, to solve this problem, but it's all fails, DFT_C1-1 error staying.

Does anyone knows how to use separate test mbist clock for testing memories with internal mux on clock port?