kcagiran

Junior Member level 1

I am electronic engineer stundent and i have an iot project thesis. I designed 2 layer pcb that reads inputs and making phone call on GSM. Teorically every single things works well. But there is huge noise when make phone call. I can hear noise PCB's and phone's speaker.

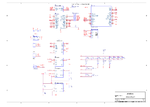

I am uploading 2 picture, 1st picture my first design and realy bad, because long and 90degree line are terrible. And my antenna line is under GSM module vcc line.

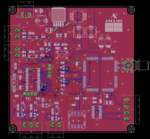

But 2nd pcb design is better, but still i have noise problem.

Please help me about solving this problem. I really need your any suggestions and any advice.

Thank you!

I am uploading 2 picture, 1st picture my first design and realy bad, because long and 90degree line are terrible. And my antenna line is under GSM module vcc line.

But 2nd pcb design is better, but still i have noise problem.

Please help me about solving this problem. I really need your any suggestions and any advice.

Thank you!