engr_joni_ee

Advanced Member level 3

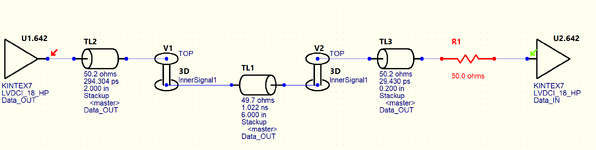

I am running a simulation on a 50 ohm transmission line in free form schematic in which I have a driver and receiver and a transmission line in between. There are also two via on the transmission line. I am running s-parameter analysis. I have attached two graphs at TDR impedance measured at driver node and TDR impedance measurement at the receiver node. What these graphs shows us ? The impedance is not 50 ohm. Is that due to the termination ?