quocviet19501

Newbie level 6

Hi all, in my system verilog project. I am stuck because of a signal below

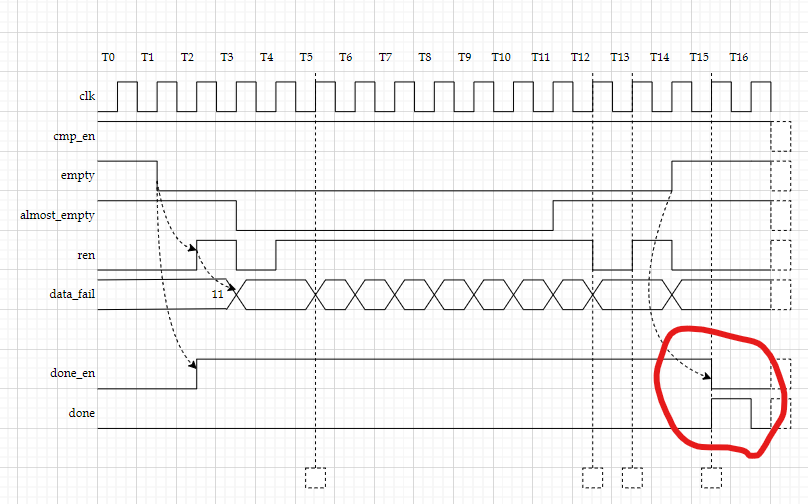

In this design, done_en is a flag that keeps tract of the generation of 2 bit data_fail. When the generation complete, the done signal asserts for 1 clk cycle to indicate data generation is finished. But I cannot find any way to control this signal like the above diagram.

Please if anyone provide any hint, I would really appreciate it.

In this design, done_en is a flag that keeps tract of the generation of 2 bit data_fail. When the generation complete, the done signal asserts for 1 clk cycle to indicate data generation is finished. But I cannot find any way to control this signal like the above diagram.

Please if anyone provide any hint, I would really appreciate it.