ben5243

Member level 3

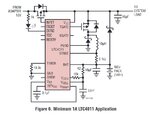

I've built an LTC4011 circuit, schematic here:

Everything works but the FETs get scorching hot in seconds.

I had previously built another with FDD6637 and SUD50N04-8M8P-4GE3 FETs which also got hot but not as bad, these were supposed to make less heat, not more

So these new FETs should theoretically create less heat and be more efficient, right?

Is this possibly a reverse recovery problem? Or current shoot-through?

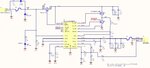

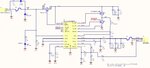

Also attached is the relevant layout of the components.

Everything works but the FETs get scorching hot in seconds.

PMOS = Si7145DP

NMOS = SiR422DP

Choke = 7447709100

LTC4011 Datasheet

Vin = 24V

Vout = 12..15V (10S nimh batt)

I had previously built another with FDD6637 and SUD50N04-8M8P-4GE3 FETs which also got hot but not as bad, these were supposed to make less heat, not more

PMOS:

Old Rds_ON = 18mR

New Rds_ON = 3.8mR

Old Rja = 40 C/W

New Rja = 20 C/W

NMOS:

Old Rds_ON = 10.5mR

New Rds_ON = 6.6mR

Old Rja = 40 C/W

New Rja = 25 C/W

So these new FETs should theoretically create less heat and be more efficient, right?

Is this possibly a reverse recovery problem? Or current shoot-through?

Also attached is the relevant layout of the components.