yefj

Advanced Member level 5

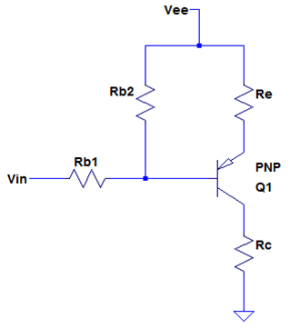

Hello, i have a PNP 2N5087 component which is connected as shown bellow.

for forward active PNP we need the Emitter-base forward biased and base-collector reversed biased.

(emitter)P-N(base) needs to be V_E>V_B to forward biased.

(base)N-P(collector) reversed biased V_base>V_collector.

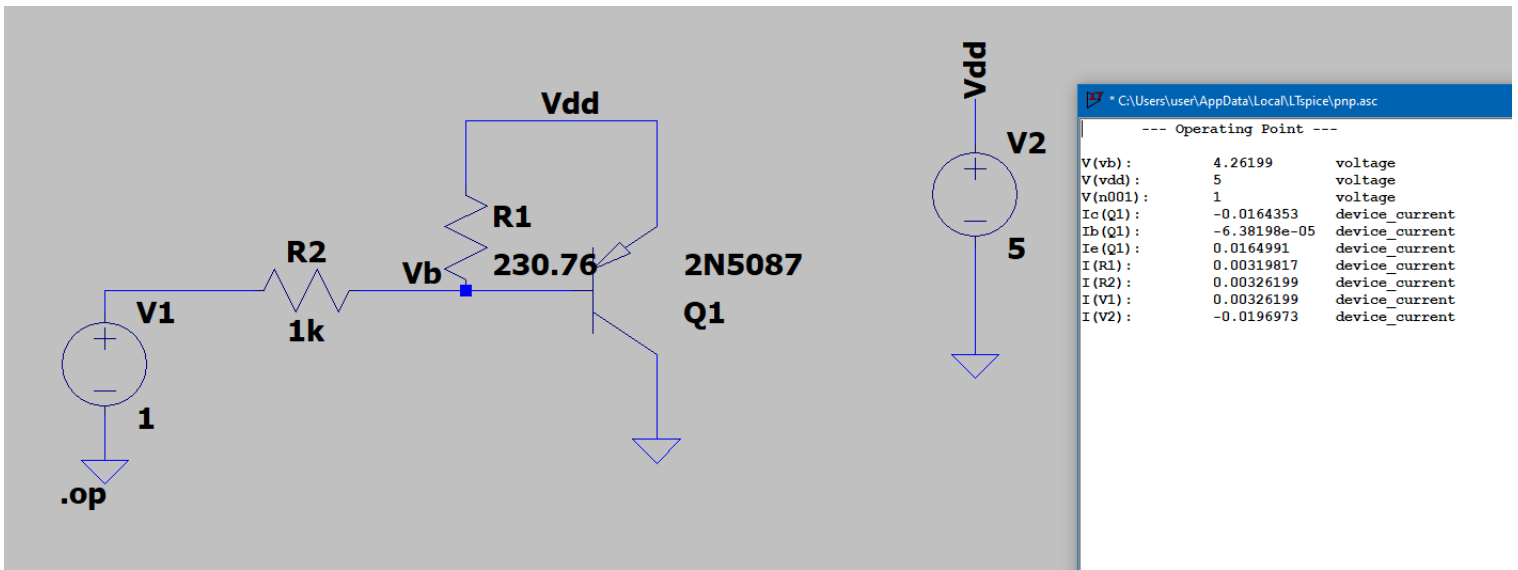

The base is a voltage divider between V1 and VDD.

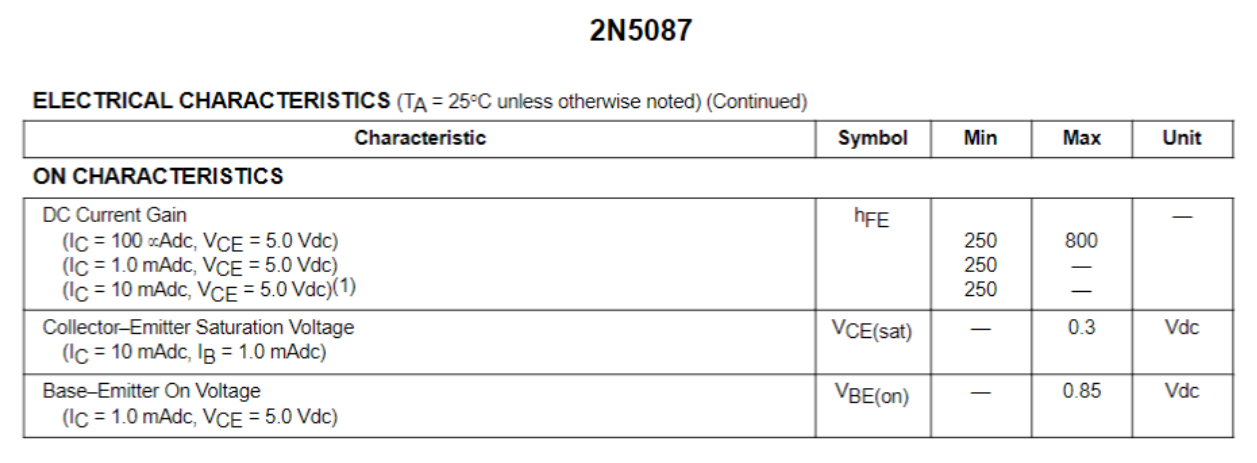

given the datasheet bellow Vbe=0.85 .

but its wrong it should be Veb=0.85 for active region.

i know that the difference between active and saturation is the Vce voltage drop.

how do i put in saturated region my PNP transistor?

should i change my circuit to be able to change the bias from forward active to saturared?

Thanks.

https://pdf1.alldatasheet.com/datasheet-pdf/view/11478/ONSEMI/2N5087.html

for forward active PNP we need the Emitter-base forward biased and base-collector reversed biased.

(emitter)P-N(base) needs to be V_E>V_B to forward biased.

(base)N-P(collector) reversed biased V_base>V_collector.

The base is a voltage divider between V1 and VDD.

given the datasheet bellow Vbe=0.85 .

but its wrong it should be Veb=0.85 for active region.

i know that the difference between active and saturation is the Vce voltage drop.

how do i put in saturated region my PNP transistor?

should i change my circuit to be able to change the bias from forward active to saturared?

Thanks.

https://pdf1.alldatasheet.com/datasheet-pdf/view/11478/ONSEMI/2N5087.html