viperpaki007

Full Member level 5

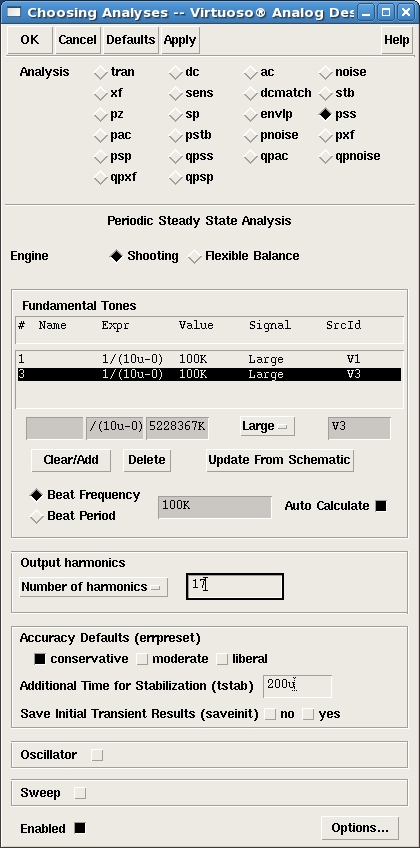

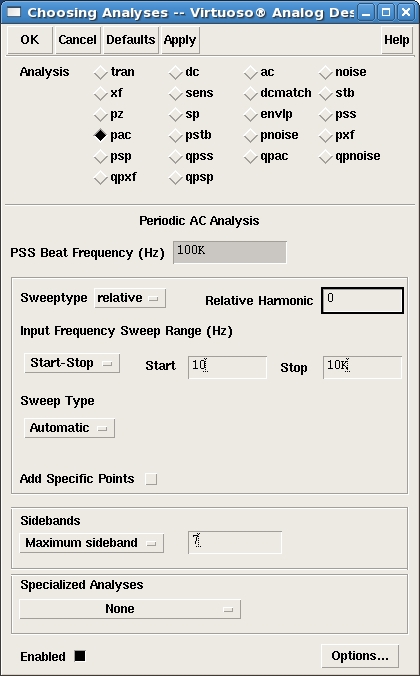

Hi,

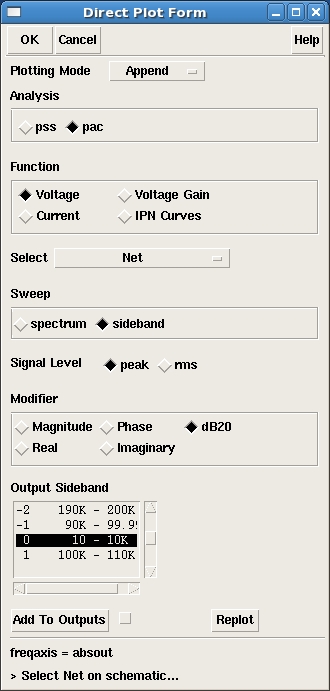

I am planning to use cadence spectre RF tool to simulate switched capacitor circuits response. Can any body suggest me a link or book to know the simulation settings/tutorial for that...

I am planning to use cadence spectre RF tool to simulate switched capacitor circuits response. Can any body suggest me a link or book to know the simulation settings/tutorial for that...