danadakk

Advanced Member level 6

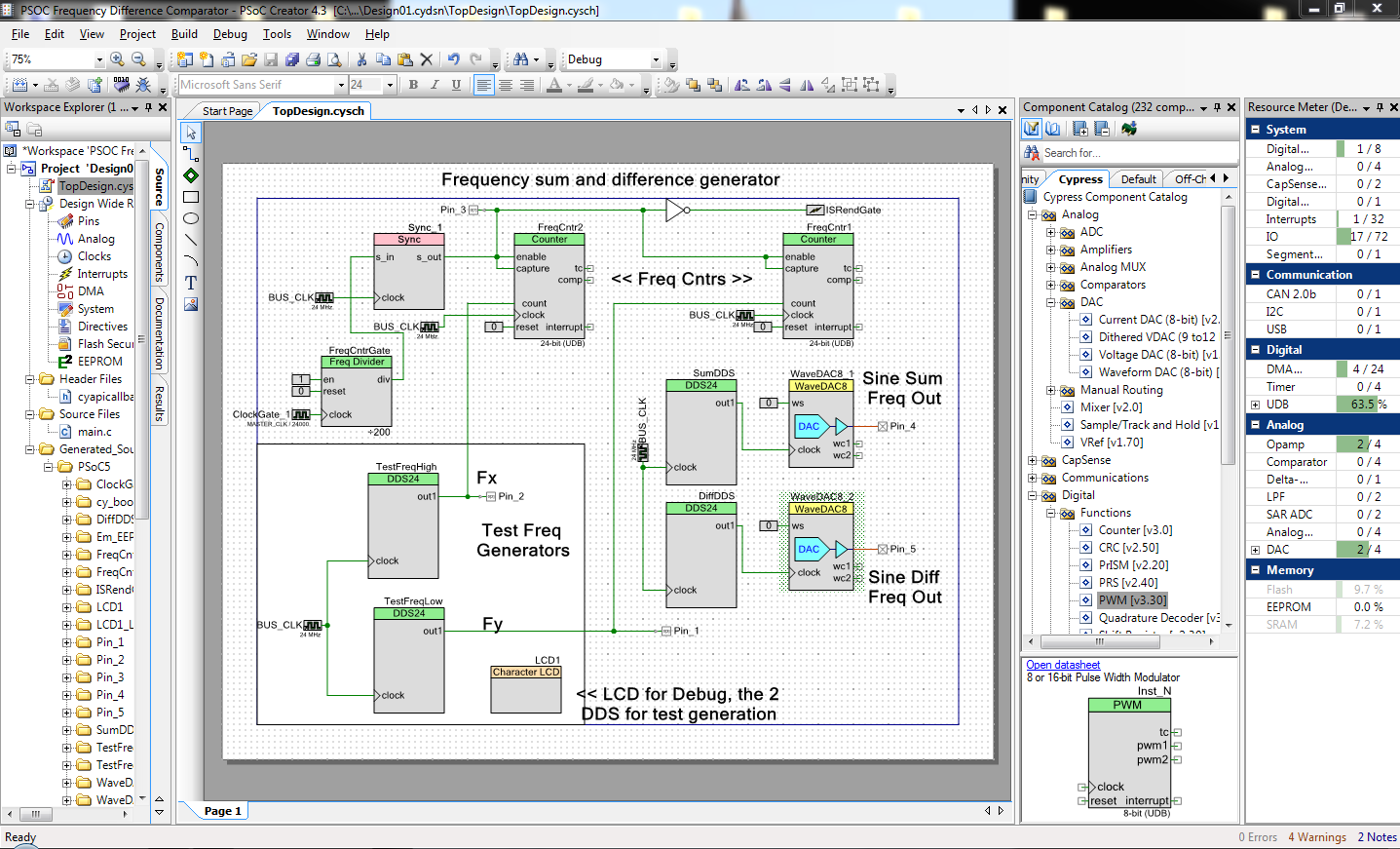

A requirement came up for a design that needed to take an Fx and Fy input signal, and

generate the sum and difference freqs, then output as sine waves.

This is a general single chip approach. Basically the input signal periods are measured, the

sum and diff calculated, and then fed to an output DDS's to generate the Wavedac's clock.

Uses PSOC 5LP chip. The Wavedac is nothing more than DMA hardware feeding a table

of waveform data to internal DAC. So a wide variety of output sum and difference waveforms

can be implemented.

The approach has the latency of the math calculation and the freq cntr gate period.

Still substantial chip resources left for other uses, see right hand window, used/left resources.

Regards, Dana.

generate the sum and difference freqs, then output as sine waves.

This is a general single chip approach. Basically the input signal periods are measured, the

sum and diff calculated, and then fed to an output DDS's to generate the Wavedac's clock.

Uses PSOC 5LP chip. The Wavedac is nothing more than DMA hardware feeding a table

of waveform data to internal DAC. So a wide variety of output sum and difference waveforms

can be implemented.

The approach has the latency of the math calculation and the freq cntr gate period.

Still substantial chip resources left for other uses, see right hand window, used/left resources.

Regards, Dana.