yefj

Advanced Member level 5

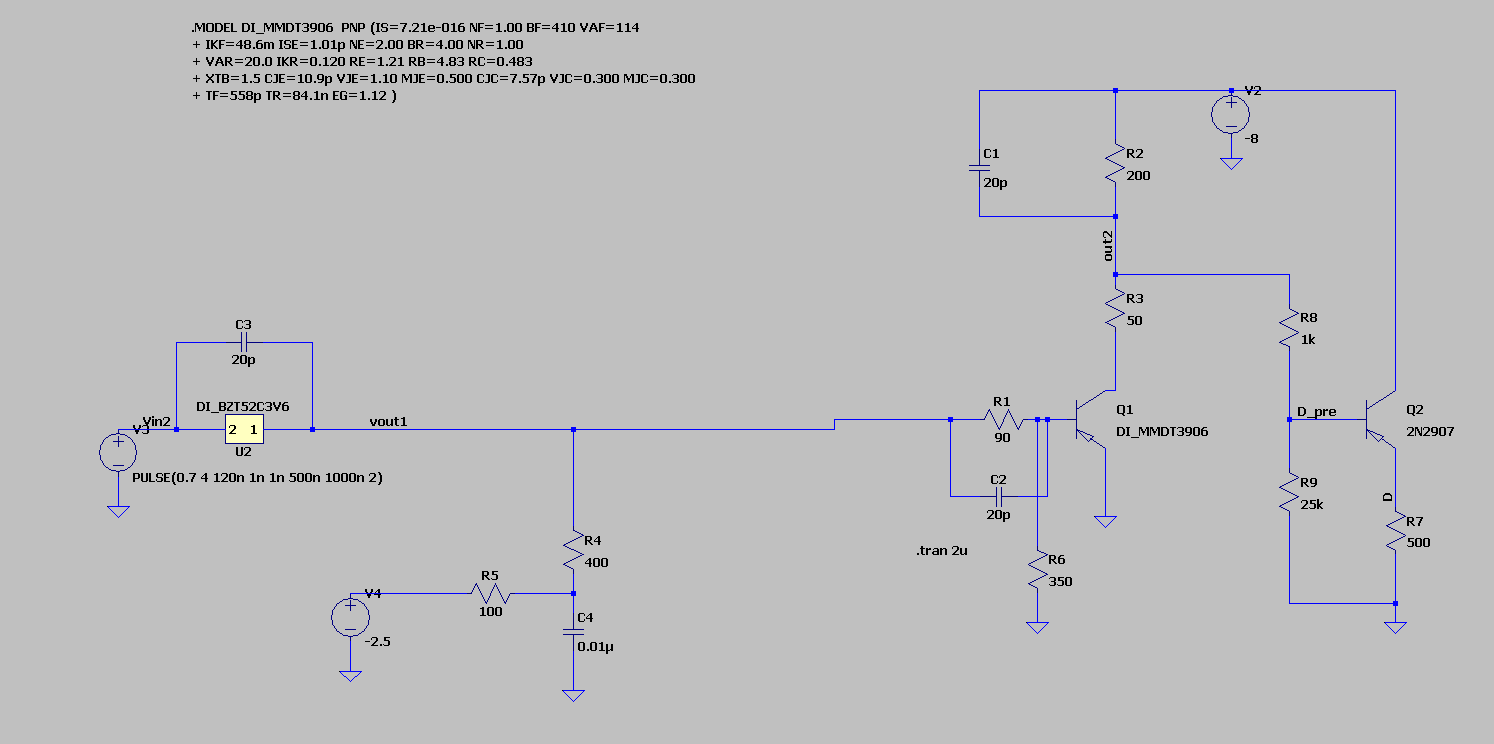

Hello, I have built the following circuit in LTSPICE.

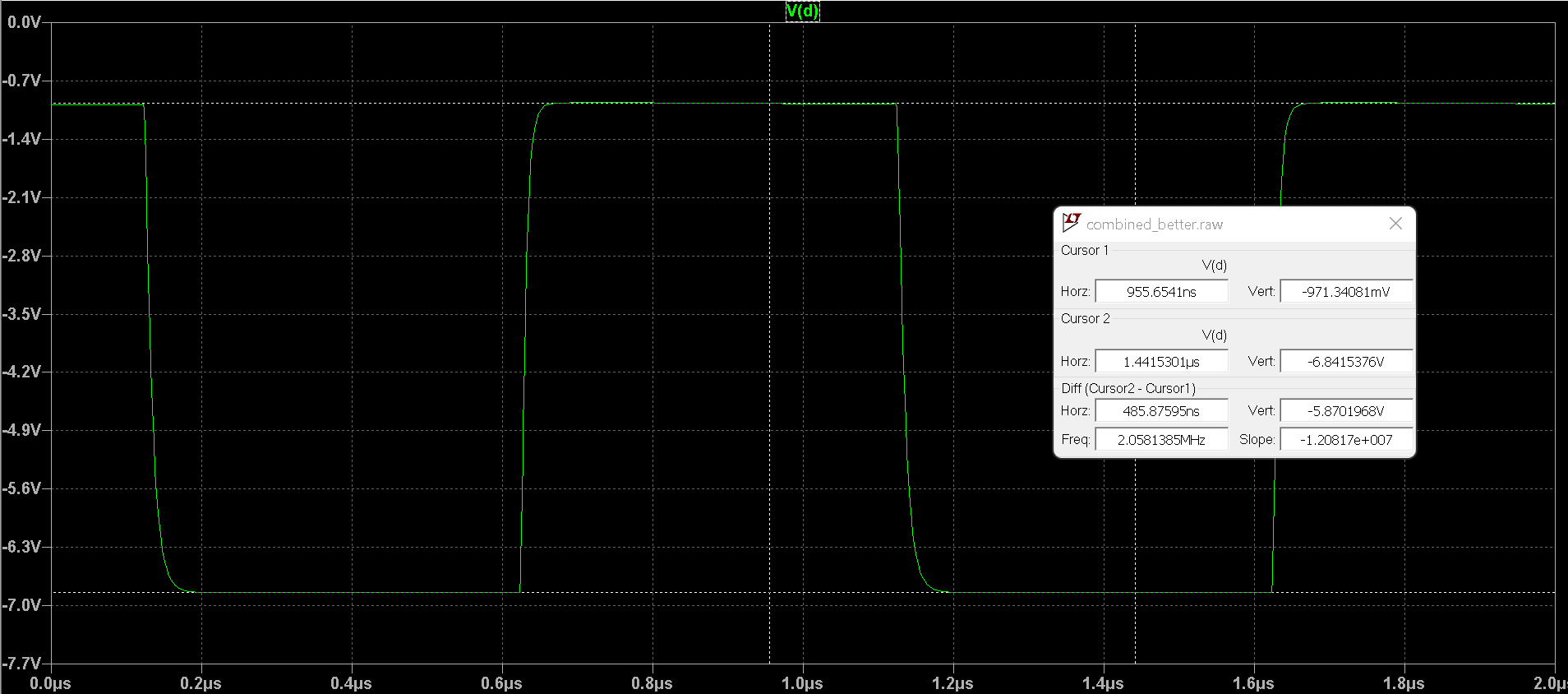

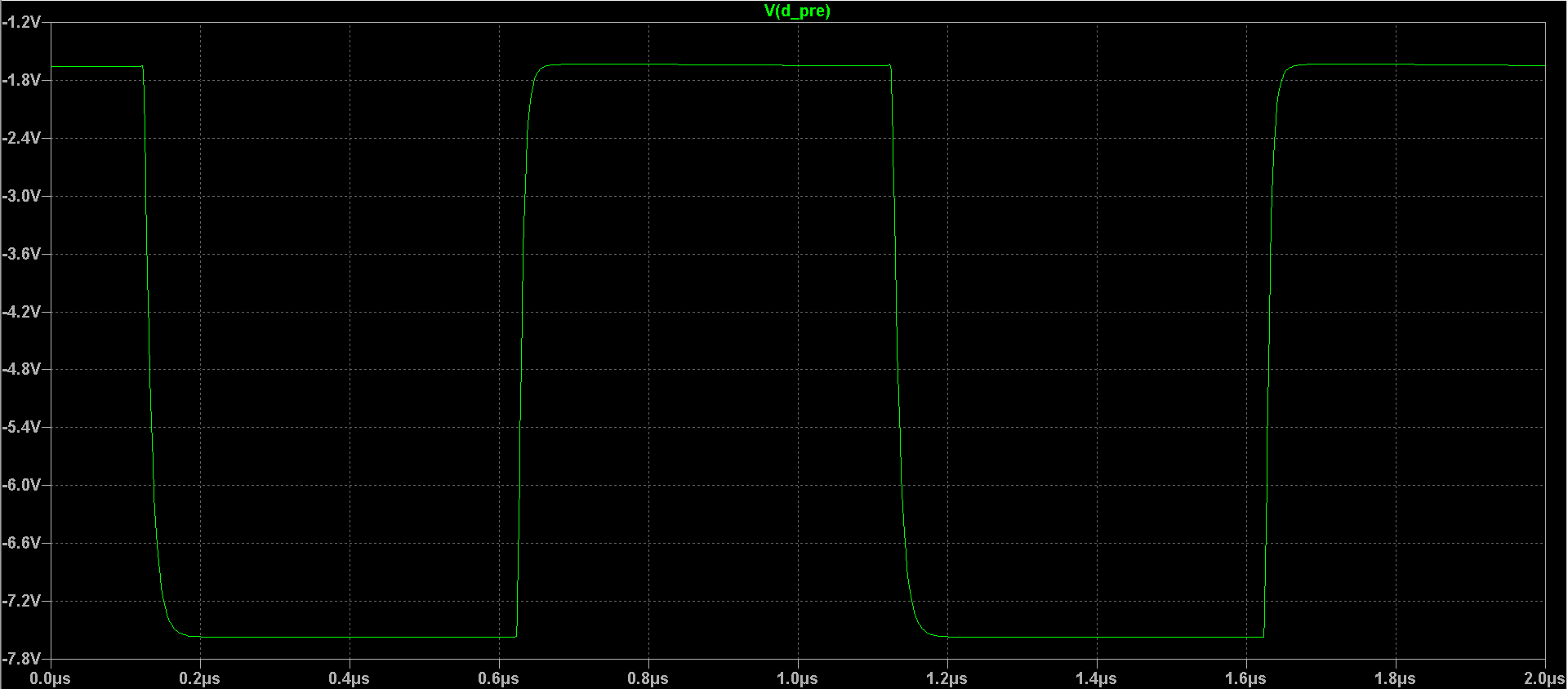

I have two nets D_pre and D plots shown below currently my pulse at D from -1 to -7 i want to change Net D pulse to be -3 to -5.

What is the strategy to do it?

Thanks.

I have two nets D_pre and D plots shown below currently my pulse at D from -1 to -7 i want to change Net D pulse to be -3 to -5.

What is the strategy to do it?

Thanks.