garimella

Full Member level 5

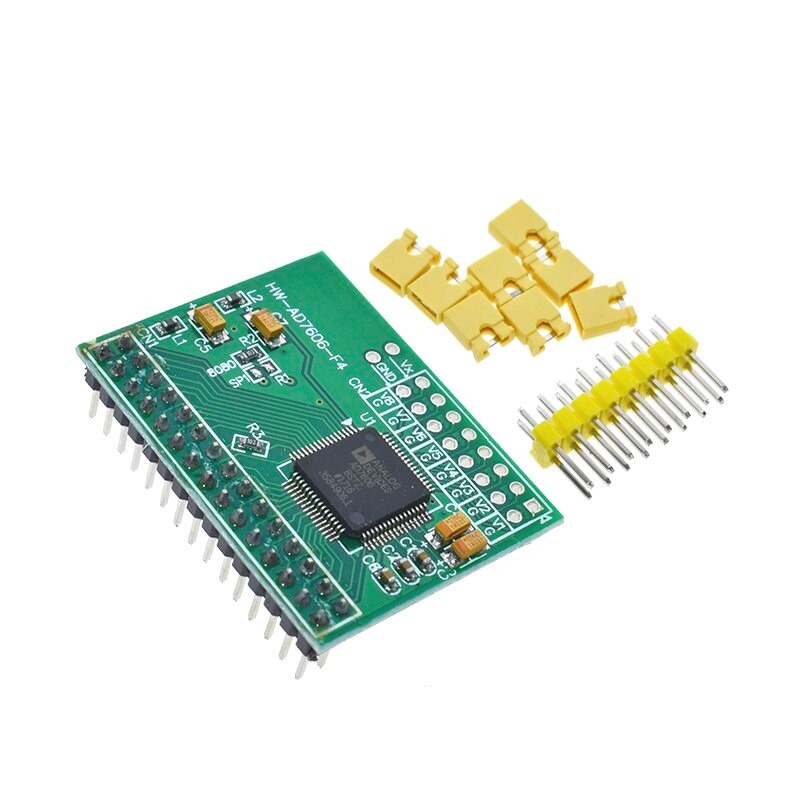

I am using a breakout board of AD7606 module. I have been using for a while without any problems. Off late I had developed a interface board to FPGA. This interface board houses ADC and translates 5V to 3.3V to FPGA. I am generating convert pulses from FPGA and mysteriously ADC module does not generate Busy pulse although FRST output pin from ADC shows up. I have changed almost 3 ADC modules and I end up in the same problem. I could not figure out the reason behind this behavior.